CUnet Family

# MKY49

DATA SHEET

**CUnet**

高速 SPI インターフェイス対応 CUnet デバイス

## MKY49 データシート

MKY49 は、MKY43 で実現していた CUnet の機能を極力継承できるよう開発されたデバイスです。

次のメモリーを持っています。

- 512Byte のグローバルメモリー (GM : Global Memory) 領域

- 256Byte のメール送信バッファー

- 256Byte × 2 のメール受信バッファー

また、次の端子を持っています。

- 1 つの割込み端子

- パブリックフレーム (PF : Public Frame) 期間を示す出力端子

- 3 つの LED 出力端子

- 4 ビットの汎用出力端子

- 4 ビットの汎用入力端子

但し MKY43 から以下の機能が削除されています。

- 1 つの割込み端子

- #CYCT 出力信号

- #PING 出力信号

- UTY1 端子、UTY2 端子

- データ検出機能 (DR : Data Renewal)

CPU インターフェイスとして、QuadSPI (Quad Serial Peripheral Interface) を採用することで、小さいパッケージでありながら、高速のアクセスを実現しています。

本資料は、“CUnet 導入ガイド”、“CUnet テクニカルガイド”、“MKY49 リファレンスマニュアル”を既にお読みになっていることを前提に記述させていただきます。まずはこれらの資料を熟読いただけますようお願いします。

## 目 次

|                                      |      |

|--------------------------------------|------|

| 1. 概要 .....                          | 1-1  |

| 1.1. 型番 .....                        | 1-1  |

| 1.2. 端子 .....                        | 1-1  |

| 1.2.1. 端子配置図 .....                   | 1-1  |

| 1.2.2. 端子機能表 .....                   | 1-2  |

| 1.2.3. 電気的定格 .....                   | 1-3  |

| 1.3. 回路設計上の注意事項 .....                | 1-4  |

| 1.3.1. 使用上の注意 .....                  | 1-4  |

| 1.3.2. 端子の処理 .....                   | 1-4  |

| 1.3.3. 未使用端子の処理 .....                | 1-5  |

| 1.3.4. 電源に関する注意 .....                | 1-5  |

| 1.3.5. リセット時の端子状態 .....              | 1-6  |

| 1.3.6. 振動子の接続 .....                  | 1-6  |

| 1.3.7. 電源投入時の制約 .....                | 1-7  |

| 2. CPU インターフェイス .....                | 2-8  |

| 2.1. SPI コマンド .....                  | 2-8  |

| 2.1.1. Read .....                    | 2-8  |

| 2.1.2. Write .....                   | 2-8  |

| 2.2. 基本動作 .....                      | 2-9  |

| 2.2.1. SingleSPI モード .....           | 2-10 |

| 2.2.2. QuadSPI モード .....             | 2-11 |

| 2.3. アクセス速度 .....                    | 2-11 |

| 2.4. 配線する際の注意点 .....                 | 2-12 |

| 3. 電気的特性 .....                       | 3-1  |

| 3.1. 絶対最大定格 .....                    | 3-1  |

| 3.2. 動作条件 .....                      | 3-2  |

| 3.2.1. 動作電源電圧 .....                  | 3-2  |

| 3.2.2. 発振端子 .....                    | 3-2  |

| 3.2.3. 外部クロック入力 OSC1(OSC0 は開放) ..... | 3-3  |

| 3.3. DC 特性 .....                     | 3-4  |

| 3.3.1. 動作電源電流 .....                  | 3-4  |

| 3.3.2. 入力端子 1 (Type-A) .....         | 3-4  |

| 3.3.3. 入力端子 2 (Type-B) .....         | 3-5  |

| 3.3.4. 入力端子 3 (Type-C) .....         | 3-5  |

| 3.3.5. 入出力端子 1 (Type-D) .....        | 3-5  |

| 3.3.6. 入出力端子 2 (Type-E) .....        | 3-6  |

| 3.3.7. 入出力端子 3 (Type-F) .....        | 3-6  |

| 3.3.8. 出力端子 1 (Type-G) .....         | 3-7  |

| 3.4. アナログ特性 .....                    | 3-8  |

| 3.4.1. 内部発振 .....                    | 3-8  |

| 3.4.2. パワーオンリセット .....               | 3-8  |

| 3.5. AC 特性 .....                     | 3-9  |

| 3.5.1. リセット .....                    | 3-9  |

|                          |      |

|--------------------------|------|

| 3.5.2. SPI インターフェイス..... | 3-10 |

| 3.5.3. 転送レートタイミング .....  | 3-11 |

| 4. 付録 .....              | 4-1  |

| 4.1. パッケージ外形寸法 .....     | 4-1  |

| 4.2. QFN 用参考基板ランド図.....  | 4-2  |

| 4.3. 実装推奨条件 .....        | 4-4  |

# 1. 概要

## 1.1. 型番

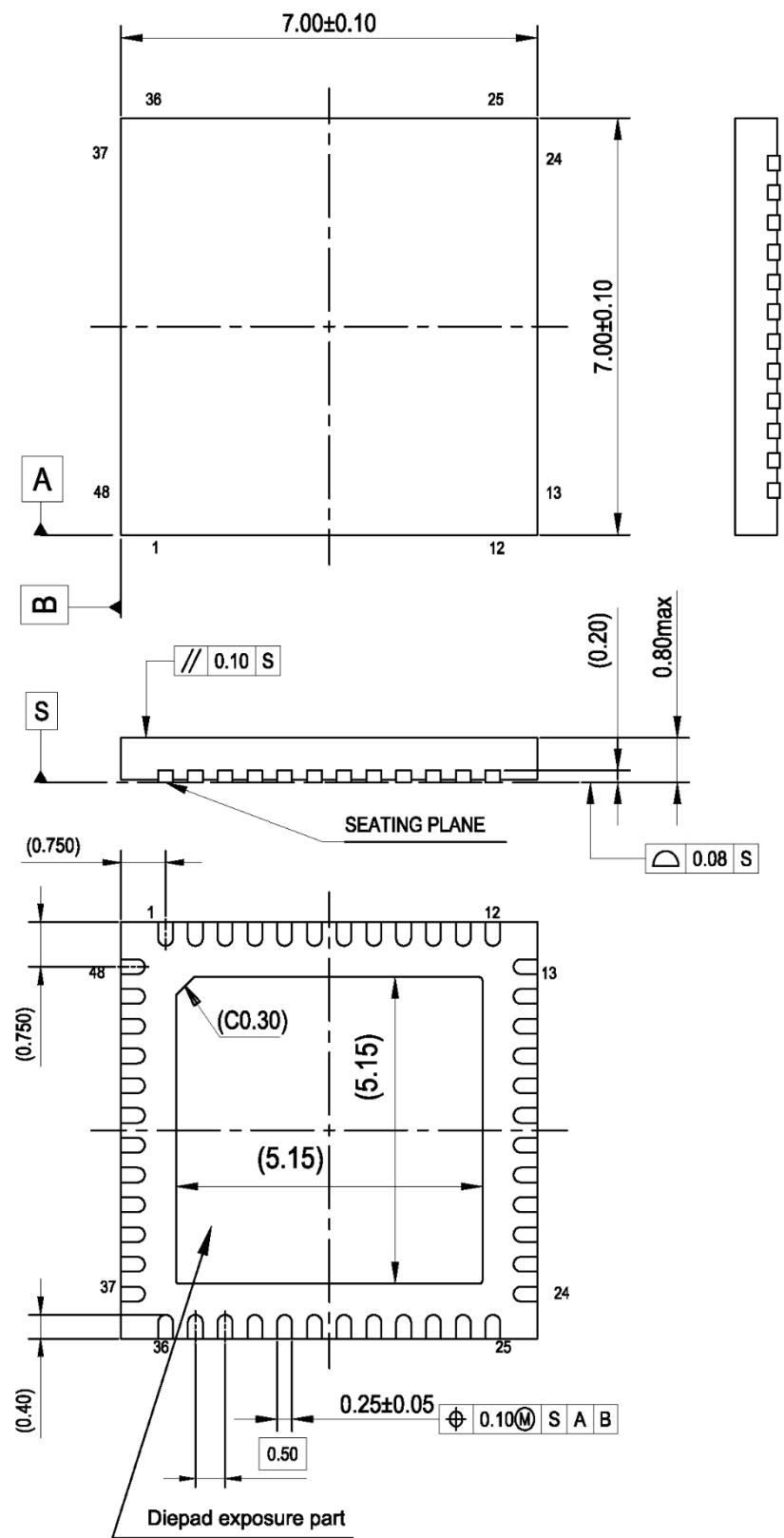

MKY49 は、型番が “MKY49” の 48pin QFN パッケージです。

## 1.2. 端子

MKY49 の端子の仕様について、次の順に示します。

- 端子配置図

- 端子機能表

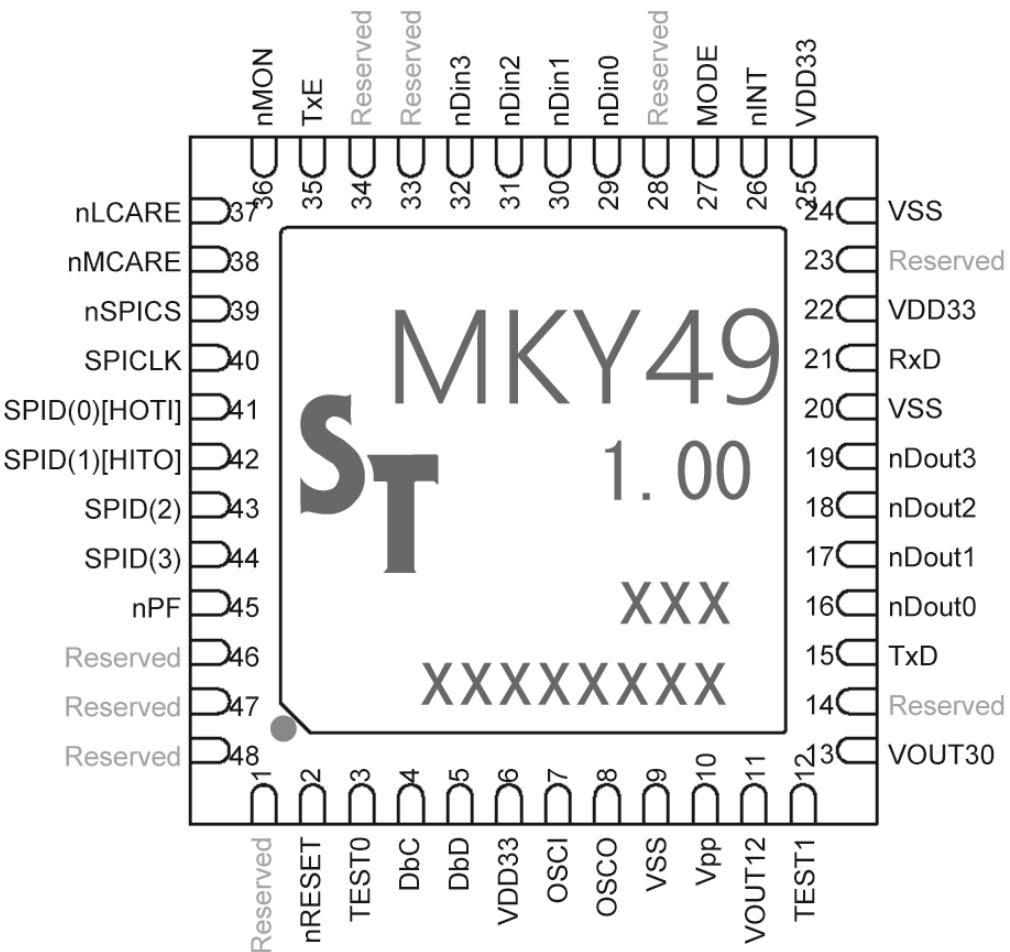

### 1.2.1. 端子配置図

48pin QFN パッケージの端子配置は次の通りです。

図 1-1 端子配置図

## 1.2.2. 端子機能表

48pin QFN パッケージの端子機能は次の通りです。

表 1-1 端子機能表

| 端子名           | 端子番号 | 論理 | I/O | 端子Type | 機能                                                                                                                                        |

|---------------|------|----|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------|

| nRESET        | 2    | 負  | I/O | D      | ハードウエアリセット入力端子です。<br>電源投入時、デバイス内部の初期化が完了するまでは Lo レベルを出力します。                                                                               |

| OSCI          | 7    | 正  | I/O | --     | 駆動クロック入力端子です。<br><b>10MHz</b> のクロックを入力してください。<br>振動子を使用する場合は OSC0 との間に接続してください。<br>発振器を使用する場合はこちらに接続してください。                               |

| OSCO          | 8    | 正  | I/O | --     | 振動子を使用する場合の駆動クロック用出力端子です。<br>発振器を使用する場合は未接続にしてください。                                                                                       |

| nSPICS        | 39   | 負  | I   | F      | CPU インターフェイスと接続するアクセス制御端子です。<br>リードまたはライトアクセスする際に、適切なタイミングによって本端子のレベルを Lo にしてください。                                                        |

| SPICLK        | 40   | 正  | I   | F      | CPU インターフェイスと接続するアクセス制御端子です。<br>SPI 通信の動作クロックを入力してください。                                                                                   |

| SPID(0)[HOTI] | 41   | 正  | I/O | F      | CPU インターフェイスと接続する双方向データバスです。<br>SingleSPI では、SPID(0)[HOTI]、SPID(1)[HITO]端子が有効となり、SPID(2)と SPID(3)は無効になります。この場合、SPID(2)と SPID(3)は開放してください。 |

| SPID(1)[HITO] | 42   | 正  | I/O | F      |                                                                                                                                           |

| SPID(2)       | 43   | 正  | I/O | F      |                                                                                                                                           |

| SPID(3)       | 44   | 正  | I/O | F      |                                                                                                                                           |

| MODE          | 27   | 正  | I   | F      | CPU インターフェイスのモードを切り替える端子です。<br>(Lo : SingleSPI モード、Hi : QuadSPI モード)                                                                      |

| nINT          | 26   | 負  | 0   | G      | CPU インターフェイスへ割込みトリガー信号を出力する端子です。割込みトリガーが発生している時に、Lo レベルを出力します。                                                                            |

| nPF           | 45   | 負  | 0   | G      | パブリックフレームの期間を示す出力端子です。<br>パブリックフレーム期間中に Lo レベルを出力します。                                                                                     |

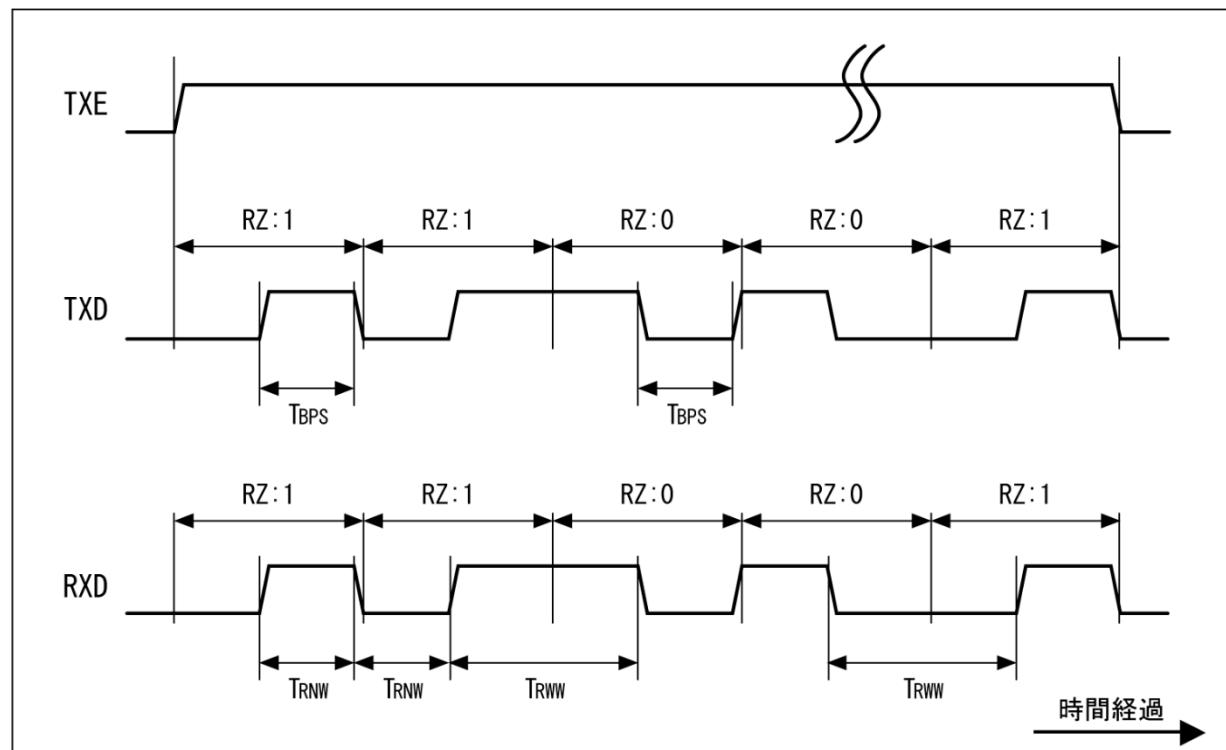

| TxE           | 35   | 正  | 0   | G      | CUnet 通信に使用される端子です。<br>パケット出力期間中に Hi レベルを出力します。<br>ドライバーのイネーブル入力端子へ接続してください。                                                              |

| TxD           | 15   | 正  | 0   | G      | CUnet 通信に使用される端子です。<br>パケットデータを出力します。<br>ドライバーなどのドライブ入力端子へ接続してください。                                                                       |

| RxD           | 21   | 正  | I   | F      | CUnet 通信に使用される端子です。<br>パケットデータを入力します。<br>レシーバーの出力端子へ接続してください。<br>レシーバーの RE をイネーブルにしてください。                                                 |

| nMON          | 36   | 負  | 0   | G      | LED 点灯用の出力端子です。                                                                                                                           |

| nLCARE        | 37   | 負  | 0   | G      |                                                                                                                                           |

| nMCARE        | 38   | 負  | 0   | G      |                                                                                                                                           |

| nDout0        | 16   | 負  | 0   | G      |                                                                                                                                           |

| nDout1        | 17   | 負  | 0   | G      | 汎用出力用の端子です。                                                                                                                               |

| nDout2        | 18   | 負  | 0   | G      |                                                                                                                                           |

| nDout3        | 19   | 負  | 0   | G      |                                                                                                                                           |

| nDin0         | 29   | 負  | I   | C      |                                                                                                                                           |

| nDin1         | 30   | 負  | I   | C      | 汎用入力用の端子です。                                                                                                                               |

| nDin2         | 31   | 負  | I   | C      |                                                                                                                                           |

| nDin3         | 32   | 負  | I   | C      |                                                                                                                                           |

| 端子名      | 端子番号 | 論理 | I/O | 端子Type | 機能                            |

|----------|------|----|-----|--------|-------------------------------|

| Reserved | 1    | -- | --  | F      | 未定義の端子です。<br>開放してください。        |

| Reserved | 14   | -- | --  | F      |                               |

| Reserved | 23   | -- | --  | F      |                               |

| Reserved | 28   | -- | --  | F      |                               |

| Reserved | 33   | -- | --  | F      |                               |

| Reserved | 34   | -- | --  | F      |                               |

| Reserved | 46   | -- | --  | F      |                               |

| Reserved | 47   | -- | --  | F      |                               |

| Reserved | 48   | -- | --  | F      |                               |

| VDD33    | 6    | -- | --  | --     | 電源端子。<br>3.3V の外部電源へ接続してください。 |

|          | 22   | -- | --  | --     |                               |

|          | 25   | -- | --  | --     |                               |

| VSS      | 9    | -- | --  | --     | 電源端子。<br>共通 GND で短絡してください。    |

|          | 20   | -- | --  | --     |                               |

|          | 24   | -- | --  | --     |                               |

| Vpp      | 10   | -- | --  | --     | 内部フラッシュ ROM のプログラム端子です。       |

| VOUT12   | 11   | -- | --  | --     | 内部レギュレーターの電圧モニタ出力です。          |

| VOUT30   | 13   | -- | --  | --     | 内部レギュレーターの電圧モニタ出力です。          |

| TEST0    | 3    | 正  | I   | A      | デバイスのテスト用端子です。                |

| TEST1    | 12   | 正  | I   | B      |                               |

| DbC      | 4    | 正  | I   | B      | デバイス内部機能で使用している端子です。          |

| DbD      | 5    | 正  | I/O | E      |                               |

### 1.2.3. 電気的定格

表 1-2 一般定格

| 項目               |                   | 端子タイプ   |     |                                     |            |            |            |            |

|------------------|-------------------|---------|-----|-------------------------------------|------------|------------|------------|------------|

|                  |                   | A       | B   | C                                   | D          | E          | F          | G          |

| $V_{IH}(V)$      | 入力電圧ハイレベル         |         |     | $0.7 \times V_{DD33} \sim V_{DD33}$ |            |            |            |            |

| $V_{IL}(V)$      | 入力電圧ローレベル         |         |     | $V_{SS} \sim 0.3 \times V_{SS}$     |            |            |            |            |

| $I_{LK}(\mu A)$  | 入力リーコンデンサー電流(max) | $\pm 5$ |     | $\pm 10$                            |            |            | $\pm 5$    |            |

| $V_{OH}(V)$      | 出力電圧ハイレベル(min)    |         |     |                                     |            | 2.8~       | 2.8~       | 2.8~       |

| $V_{OL}(V)$      | 出力電圧ローレベル(max)    |         |     |                                     | $\sim 0.5$ | $\sim 0.5$ | $\sim 0.5$ | $\sim 0.5$ |

| $I_{OL}(mA)$     | 出力電流              |         |     |                                     | 2          | $\pm 4$    | $\pm 4$    | $\pm 4$    |

| $R_{IO}(\Omega)$ | 内蔵 PullUp 抵抗(typ) | -       | 30K | -                                   | 30K        | 30K        | 30K        | -          |

## 1.3. 回路設計上の注意事項

### 1.3.1. 使用上の注意

本LSIを使用する上で、以下の注意事項を遵守してください。

- 1) 動作条件を確認の上、使用してください。保証温度の範囲を超えた温度で使用する場合、動作マージンがなく誤動作する恐れがあります。

- 2) 動作条件を確認の上、使用してください。

- 保証電圧より高い電圧で使用した場合、信頼性保証(経時変化によるトランジスターの寿命保証等)がでません。

- 保証電圧より低い電圧で使用した場合、動作マージンがなく誤動作する恐れがあります。

- 3) 高電界の加わる場所で使用する場合は、正常動作保証のためにパッケージ表面をシールドしてください。

### 1.3.2. 端子の処理

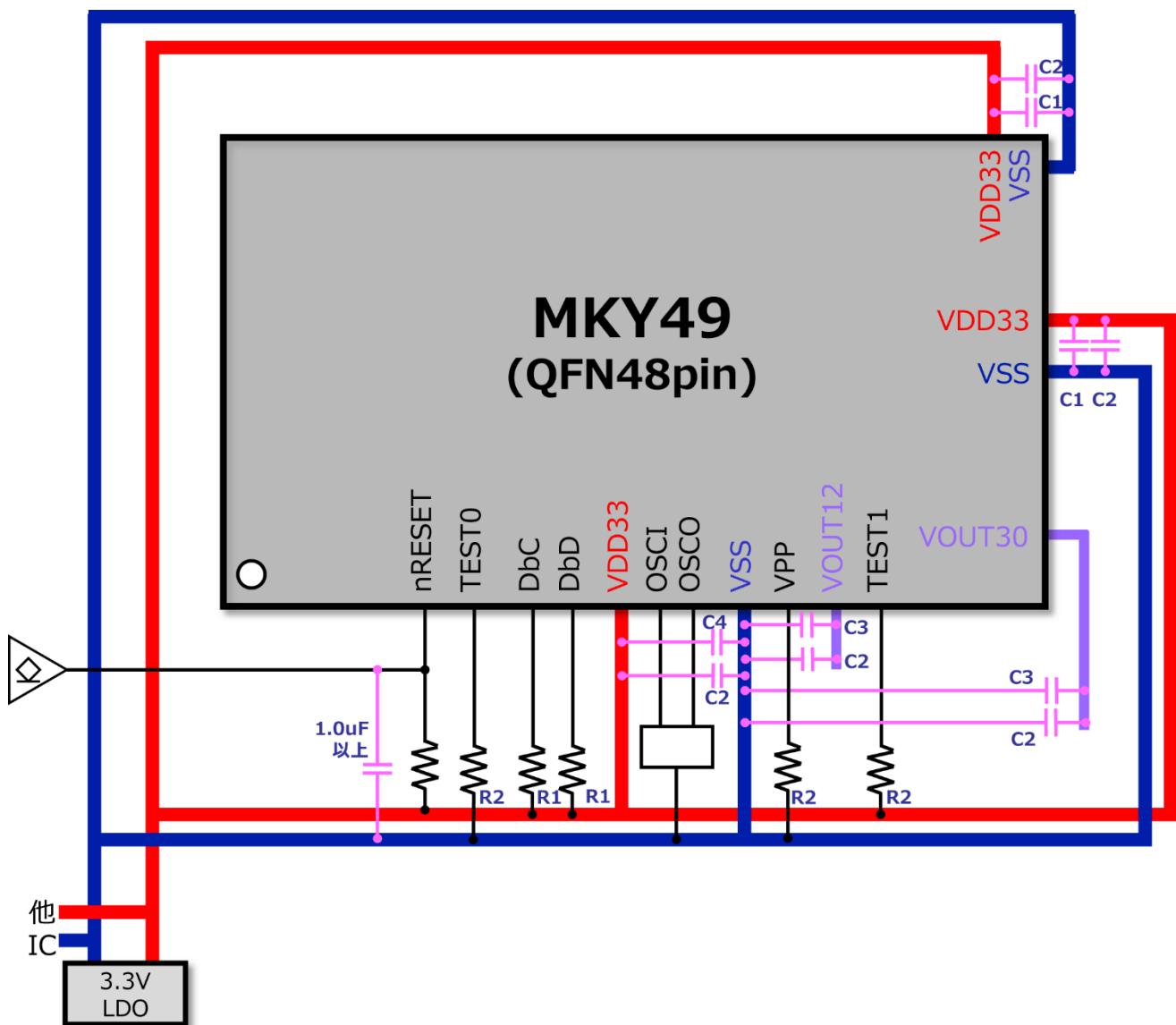

次の図 1-2 を参考に回路設計を行ってください。

図 1-2 参考回路図ブロック図

端子の処理について、下表に示します。

表 1-3 端子処理一覧

| 端子名              | 端子属性 | 処理内容                                                                                                                      |

|------------------|------|---------------------------------------------------------------------------------------------------------------------------|

| VDD33            | 入力   | 3V 系の外部電源へ接続してください。<br>各端子 - VSS 間に<br>バイパスコンデンサー : 0.1 $\mu$ F と<br>デカップリングコンデンサー : 10 $\mu$ F 以上を<br>接続してください。(端子近傍に配置) |

| VSS              | 入力   | 共通 GND で短絡させてください。                                                                                                        |

| VOUT30<br>VOUT12 | 出力   | 各端子 - VSS 間に<br>バイパスコンデンサー : 0.1 $\mu$ F と<br>安定化用コンデンサー : 10 $\mu$ F ~ 50 $\mu$ F を<br>接続してください。(端子近傍に配置)                |

| OSCI<br>OSCO     | 入出力  | OSCI、OSCO 端子に振動子を接続し、外部発振を起動させることでクロックが生成されます。                                                                            |

| DbC, DbD         | 入出力  | 10 k $\Omega$ の抵抗で VDD33 へプルアップ接続してください。                                                                                  |

| TEST1            | 入力   | 2 k $\Omega$ の抵抗で VDD33 へプルアップ接続してください。                                                                                   |

| TEST0, Vpp       | 入力   | 2 k $\Omega$ の抵抗で VSS へプルダウン接続してください。                                                                                     |

| nRESET           | 入出力  | 外部コネクターとの間に 100 $\Omega$ の制限抵抗を挿入してください。<br>端子 - VSS 間に 1.0 $\mu$ F 以上のコンデンサーを接続してください。<br>(端子近傍に配置)                      |

各端子の処理方法は、外来ノイズ等の影響を考慮し、十分に評価を行った上で決定してください。

### 1.3.3. 未使用端子の処理

ご使用にならない出力端子は開放する事を推奨します。

ご使用にならない入力端子は次のいずれかの処理を行ってください。

- VSS へのプルダウン抵抗接続

- VDD33 へのプルアップ抵抗接続

外部で追加処理される場合は、外来ノイズ等の影響を考慮し、十分に評価を行った上で決定してください。

### 1.3.4. 電源に関する注意

電源に関する注意として次の項目があります。

- デバイスの電源 (VDD33) と入力端子電圧の関係

入力端子電圧は、デバイスの電源が立上がった後に供給されるようにしてください。順番が逆転すると、デバイス内部でラッチアップが発生し、大電流による破壊の恐れがあります。

- デバイスの電源回路について

電源回路は、AC ラインノイズなどの評価、および LED などの駆動時のリップル状態を確認のうえ、電源方式を検討し、十分余裕のある設計を行ってください。

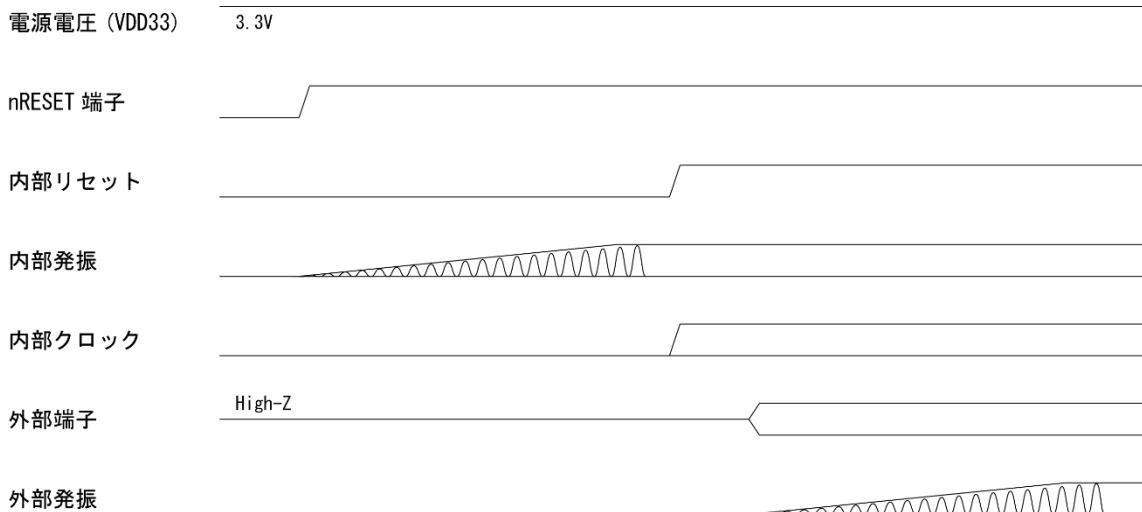

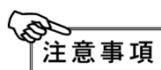

### 1.3.5. リセット時の端子状態

nRESET 端子が Lo になっているとリセット状態となります。

このとき、入力端子・出力端子は、ハイインピーダンス状態となっています。

図 1-3 リセット時のシーケンス

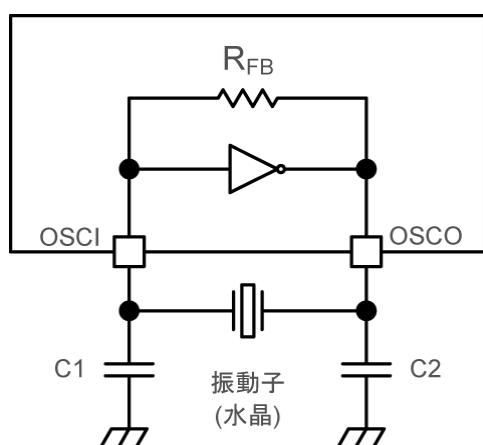

### 1.3.6. 振動子の接続

MKY49 の外部発振には、水晶振動子を使用することができます。振動子の接続例を図 1-4 に示します。

図 1-4 振動子接続図

OSCI/OSCO 端子に接続する振動子の回路定数は、振動子、実装回路の浮遊容量などにより異なる為、必ず振動子メーカーと十分ご相談の上、決定してください。

なお、発振器を使用される場合は、OSCI 端子に信号を入力し OSCO 端子は開放してお使いください。

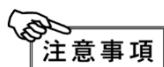

### 1.3.7. 電源投入時の制約

本デバイスは、パワーオンリセットにより電源投入時にリセットが発生します。また、内部レギュレーターで生成した内部電源が動作します。

図 1-5 電源投入時の電圧推移

minVRST33P : 電源電圧検知レベル

minVOUT30 : VOUT30 下限レベル (2.70V)

minVOUT12 : VOUT12 下限レベル (1.08V)

t<sub>VOUT12</sub> : 電源電圧が投入された後、内部電源電圧 VOUT12 が 1.08V に達するまでの時間

t<sub>VOUT30</sub> : 電源電圧が投入された後、内部電源電圧 VOUT30 が 2.70V に達するまでの時間

t<sub>VRST</sub> : 電源電圧が、電源電圧検知レベルの下限に達するまでの時間

t<sub>nRSTW</sub> : nRESET 端子の Lo レベルを維持する時間

nRESET 端子の電圧・電源電圧 (VDD33)、及び内部電源電圧 (VOUT30・VOUT12) の関係が下記条件を遵守するよう、電源設計をしてください。

$0.2\text{msec}/V \leq \Delta t_{VDD33P}$  1V 立上るのに 0.2msec 以上の時間をかけること

$t_{VOUT30} < t_{VRST}$  VOUT30 よりも VDD33 の検知が後ろになること

$t_{VOUT12} < t_{VRST}$  VOUT12 よりも VDD33 の検知が後ろになること

$t_{nRSTW} \geq 1\mu\text{sec}$  VDD33 の検知の後、nRESET が 1μsec 以上 Lo であること

## 2. CPU インターフェイス

MKY49 で用意している CPU インターフェイスは、SPI (Serial Peripheral Interface) です。ホストの機能は持たず、ターゲット専用として動作します。データバスとして 4 本を使用した QuadSPI モードと、入力・出力を 1 本ずつ使用した SingleSPI モードの 2 種類を持っています。このモードは、MODE 端子により切り替え可能です。MODE 端子が Lo レベルなら SingleSPI モードが、Hi レベルなら QuadSPI モードが有効になります。

ホスト (CPU) とターゲット (MKY49) は 1 対 1 で接続してください。（“[2.4 配線する際の注意点](#)”参照）

MODE 端子の状態は、電源投入後又はリセット解除されたときにのみ確認するため、動作中に切り替えることはできません。

### 2.1. SPI コマンド

MKY49 がサポートする SPI コマンドを表 2-1 に示します。

表 2-1 SPI コマンド

| コマンド | コマンド名 | 内容                     | SingleSPI<br>ダミー <sup>1</sup><br>サイクル | QuadSPI<br>ダミー <sup>1</sup><br>サイクル |

|------|-------|------------------------|---------------------------------------|-------------------------------------|

| 0x03 | Read  | 内部メモリーやレジスタのデータを読み出せます | 無                                     | 有                                   |

| 0x02 | Write | 内部メモリーやレジスタのデータを書き込みます | 無                                     | 無                                   |

#### 2.1.1. Read

指定したアドレスから 16 ビット単位でデータを読み出します。

SPICLK 端子にクロックを供給し続けることによって、バーストリードが可能です。

QuadSPI モードでは、“2” サイクルのダミービットを挿入してください（“[2.2.2 QuadSPI モード](#)” 参照）。

#### 2.1.2. Write

指定したアドレスに 16 ビット単位でデータを書き込みます。

SPICLK 端子にクロックを供給し続けることによって、バーストライトが可能です。

## 2.2. 基本動作

MKY49 の CPU インターフェイスである SPI (Serial Peripheral Interface) は、“3.5.2 SPI インターフェイス”に示された AC 特性に基づき、nSPICS 端子が Lo レベルである期間中に稼働し、Hi レベルへの遷移により 1 回のアクセスを終了します。

SPI コマンドの Read コマンド及び Write コマンドにおけるメモリーアクセスでは、nSPICS 端子のレベルを Lo に保つ事によって、連続したアクセスである「バーストリード」や「バーストライト」が可能です。アクセスの途中で nSPICS 端子が Lo レベルから Hi レベルに遷移した場合には、アクセスが中断されたものとみなされます。nSPICS 端子が Hi レベルから Lo レベルに遷移する時の、SPICLK 端子のレベルは Hi であっても Lo であっても構いません。MKY49 は、SPICLK 端子の立上りエッジによってホストからの信号ビットを取り込み、SPICLK 端子の立下がりエッジによってホストへの信号ビットを更新します。

MKY49 の SPI は、以下の特異性を持っています。

- ① “Adr.+0” における Read Data は、常に “0” として扱われます。

これは高速アクセスを目指すのと内部 16 ビット幅 RAM を利用している事からです。

よって、例えば、Address 0x0001 の 1 bytes だけを読み出す事はできません。

この場合は、“Adr.+0”、“Adr.+1” の Read Data をホストが受け取ってから、“Adr.+0” の Read Data は読み捨ててください。

なお、この回路対象の LSI 内部メモリーは、リトルエンディアン形式です。

- ② 有効アドレスは、0x0000～0x3FFF です。

0x4000 以降は、0x0000 からの巡回アドレスとして扱われます。

Address は、A[13]までが使われ、A[23:14] は参照されません。

一般的なシリアルメモリーが、業界標準として A[23] まで利用していることからそのフォーマットに整合させています。

- ③ この回路は、SPICLK 端子に供給されたクロックのエッジで入出力が駆動されています。

よって、SPICLK 端子に供給するクロックの静止やパルス幅の変化にも対応しています。

- ④ Write コマンドでは、CPU が SPID(0)～SPID(3)に出力したデータは、16 ビット単位で内部に取り込まれます。32 ビット分が取り込まれると、32 ビットアクセスによりデータが書き込まれます。16 ビット分のみ取り込まれた状態で、nSPICS 端子が Hi レベルに遷移すると、現状の 32 ビットデータをリードし、対象の 16 ビットを取り込んだデータに更新した後、32 ビットアクセスにより書き込まれます。

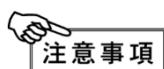

## 2.2.1. SingleSPI モード

SingleSPI モードにおけるメモリーアクセスコマンドの基本フォーマット及び基本動作について説明します。

SingleSPI モードにおけるメモリーアクセスの基本フォーマットは、“Command”、“Address”、“Data” の並びです（図 2-1 参照）。“Data” の位置で SPICLK 端子へのクロック供給を継続することでバーストアクセスになります。

SingleSPI モードにおけるメモリーアクセスは、双方向の切り替え時間がないため、ダミーサイクルの挿入は必要ありません。

Write コマンドでは、Write Data を CPU から供給します。そのとき、SPID(1)[HITO] 端子には何も現れません。Write Data は、SPID(0)[HOTI] 端子から 16 ビット単位で取り込まれ、内部のメモリーへ書き込まれます。

Read コマンドでは、Address から後の SPID(0)[HOTI] 端子は意味を持たず、SPICLK 端子に供給されるクロックによって Read Data が SPID(1)[HITO] 端子から出力されます。

【 SingleSPI Read/Write 】

図 2-1 SingleSPI モード

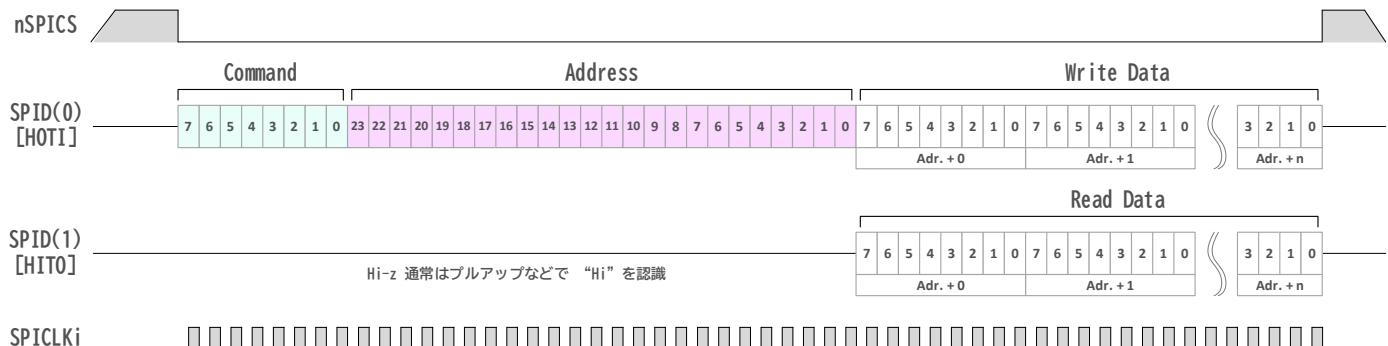

## 2.2.2. QuadSPI モード

QuadSPI モードにおけるメモリーアクセスコマンドの基本フォーマット及び基本動作について説明します。

QuadSPI モードにおけるメモリーアクセスの基本フォーマットは、“Command”、“Address”、“Data” の並びです（図 2-2 QuadSPI モード参照）。Command と Address が 4 ビットパラレル入力、Write Data 及び Read Data が 4 ビットパラレル入出力になります。“Data” の位置で SPICLK 端子へのクロック供給を継続することでバーストアクセスになります。Write コマンドでは、双方向の切り替え時間が無いため、ダミーサイクルの挿入は必要ありません。Read コマンドでは、内部動作の制約によりアドレス確定からデータ準備までの時間が必要となるため、“2” サイクルのダミーサイクルを挿入してください。

図 2-2 QuadSPI モード

## 2.3. アクセス速度

“3.5.2 SPI インターフェイス” に示された AC 特性により、SPICLK の Hi 状態と Lo 状態は 30nsec 以上である必要があることから、アクセス速度の最速は次のような値になります。

60ns. [ 30ns / 30ns ] 周期時間のクロック → 16.6MHz

図 2-1 及び図 2-2 で示すように、1 回のアクセスで Command と Address のオーバーヘッドが発生します。QuadSPI の場合、Read コマンドでダミーサイクルが 2 サイクルとするとデータが出力されるまで 10 サイクルとなります。64 ビット分の読み出しに 16 サイクル必要ですので、合計 26 サイクルとなります。

また、SPICLK に供給するクロックが最速の 16.6MHz であるとき、5Mbyte/sec ほどのアクセス速度になると思われます。したがって、速度を向上されるためには、極力バースト転送でより多くのデータを連続してアクセスすることをお薦めします。

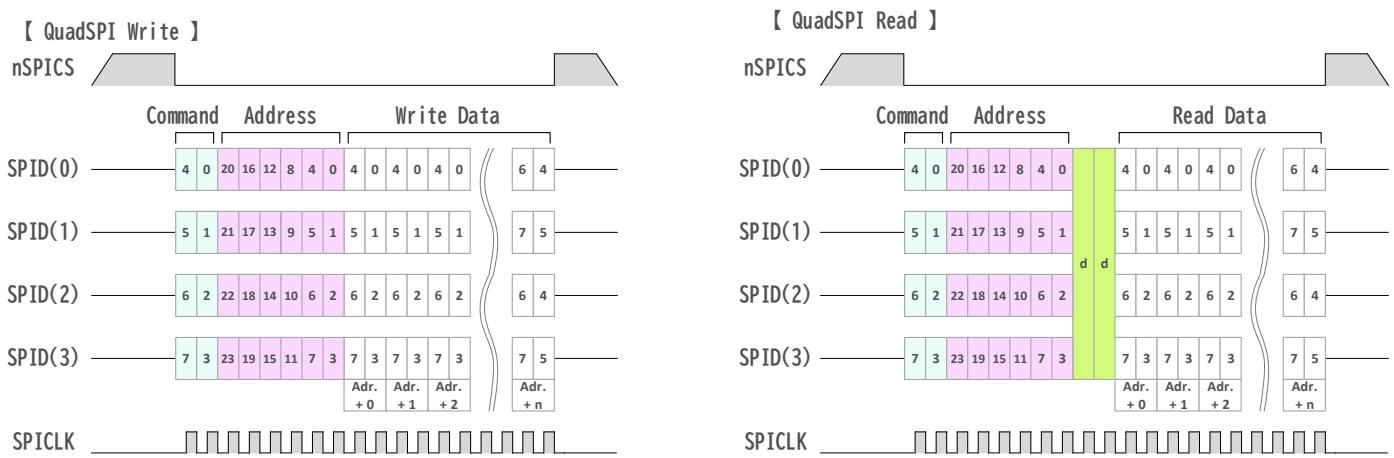

## 2.4. 配線する際の注意点

MKY49 に搭載された SPI インターフェイスは、最速 16.6MHz の高速信号に対応しています。よって、図 2-3 にある「分岐や結合の有る配線」や「デイジーチェーン配線」のような信号劣化を招く接続は行わないでください。バッファーを挿入し信号分配する場合も注意が必要です。例えば、SPI クロックが数 10KHz などの低速での利用であっても、配線上の信号伝搬にオーバーシュートやアンダーシュートが発生する状況であると、正しく動作しない原因となります。

配線には、グランドガードやダンピング抵抗を挿入するなどの高速信号に配慮したノイズ対策を施してください。ダンピング抵抗の適正值は、配線の引き回しや配線長など、基板の実行環境で変わりますので、全ての信号線 (CS, CLK, IO) に対して波形観測をしながら調整することを推奨します。

また、SPI はランダムアクセスに向いていないことからバーストリード・バーストライトでの GM 領域へのアクセスを想定しています。同じインターフェイスに他のデバイスが存在すると、排他処理が発生し、パフォーマンスが低下するため、ホスト (CPU) とターゲット (MKY49) が単独で 1 対 1 となる接続を推奨します。

図 2-3 配線する際の注意点

### 3. 電気的特性

#### 3.1. 絶対最大定格

表 3-1 絶対最大定格

$V_{SS} = 0.0 \text{ V}$

| 項目       | 略号          | 定格             |     |                                | 単位 |

|----------|-------------|----------------|-----|--------------------------------|----|

|          |             | min            | typ | max                            |    |

| 電源電圧     | $V_{DD33}$  | -0.3           |     | 7.0                            | V  |

| 内部電源電圧 1 | $V_{OUT30}$ | -0.3           |     | 4.6                            |    |

| 内部電源電圧 2 | $V_{OUT12}$ | -0.3           |     | 1.6                            |    |

| 入力端子電圧   | $V_{I1}$    | -0.3           |     | $V_{DD33} + 0.3$<br>(上限 : 7.0) |    |

| 入出力端子電圧  | $V_{I2}$    | -0.3           |     | $V_{DD33} + 0.3$<br>(上限 : 7.0) |    |

| 平均出力電流   | 入出力端子 1     | $I_{01}$ (avg) |     | $\pm 12$                       | mA |

|          | 入出力端子 2     | $I_{02}$ (avg) |     | $\pm 24$                       |    |

|          | 全端子合計       | $I_{03}$       |     | $\pm 70$                       |    |

| 許容損失     | PT          |                | 500 |                                | mW |

| 動作周囲温度   | $T_{OPR}$   | -40            |     | 85                             | °C |

| 保存温度     | $T_{STG}$   | -40            |     | 125                            |    |

本デバイスは ESD 保護回路を内蔵していますが、適切な処理を行わない場合、本製品に恒久的な損傷を与えることがあります。

MOS ゲートに対する静電破壊を避けるため、適切な ESD 予防措置が推奨されます。

また、上記の絶対最大定格を超えるストレスを瞬時でも与えた場合、本 LSI に恒久的な損傷を与えることがあります。これはストレスの定格についての規定であり、動作条件の項目に記載する値以上でのデバイス動作を保証するものではありません。

## 3.2. 動作条件

### 3.2.1. 動作電源電圧

表 3-2 動作電源電圧

$V_{SS} = 0.0 \text{ V}$ ,  $T_a = -40 \sim 85 \text{ }^{\circ}\text{C}$

| 項目       | 略号          | 許容値          |      |     | 単位 |

|----------|-------------|--------------|------|-----|----|

|          |             | min          | typ  | max |    |

| 外部電源電圧   | $V_{DD33}$  | $V_{RST33N}$ | 3.3  | 3.6 | V  |

| 内部電源電圧 1 | $V_{OUT30}$ |              | 2.9  |     |    |

| 内部電源電圧 2 | $V_{OUT12}$ |              | 1.25 |     |    |

電源電圧検出レベル  $V_{RST33N}$  については “3.4.2 パワーオンリセット特性” を参照してください。

内蔵レギュレーター出力( $V_{OUT30}$ 、 $V_{OUT12}$ )を外部の回路に供給することはできません。

### 3.2.2. 発振端子

表 3-3 発振端子

$V_{DD33} = V_{RST33N} \sim 3.6 \text{ V}$ ,  $V_{SS} = 0.0 \text{ V}$ ,  $T_a = -40 \sim 85 \text{ }^{\circ}\text{C}$

| 項目          | 略号        | 許容値 |      |     | 単位  |

|-------------|-----------|-----|------|-----|-----|

|             |           | min | typ  | max |     |

| 入力周波数       | $F_{OSC}$ |     | 10.0 |     | MHz |

| 内蔵フィードバック抵抗 | $R_{FB}$  |     | 1.0  |     | MΩ  |

周波数精度は、±500ppm以内のものをお使いください。

発振回路特性及び周辺部品（負荷容量、ダンピング抵抗、帰還抵抗）は使用する振動子・基板特性により異なります。使用する振動子メーカーにご相談ください。

図 3-1 水晶振動子接続図

MKY49 では 10MHz が入力されるとして、内部設定を行っています。

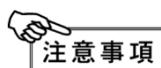

### 3.2.3. 外部クロック入力 OSC1(OSC0 は開放)

表 3-4 外部クロック入力

$V_{DD33} = V_{RST33N} \sim 3.6 \text{ V}$ ,  $V_{SS} = 0.0 \text{ V}$ ,  $T_a = -40 \sim 85 \text{ }^{\circ}\text{C}$

| 項目           | 略号        | 許容値 |      |     | 単位  |

|--------------|-----------|-----|------|-----|-----|

|              |           | min | typ  | max |     |

| クロック周波数      | $F_{CP}$  |     | 10.0 |     | MHz |

| High レベルパルス幅 | $t_{wh1}$ |     | 50   |     | ns  |

| Low レベルパルス幅  | $t_{wl1}$ |     | 50   |     |     |

| 立上がり時間       | $t_{wr1}$ |     |      | 5   |     |

| 立下がり時間       | $t_{wf1}$ |     |      | 5   |     |

クロックデューティー比は、45 % ~55 %としてください。

周波数精度は、±500ppm 以内のものをお使いください。

ジッタ成分は±500ppm 以内のものをお使いください。

図 3-2 クロックタイミング

MKY49 では **10MHz** が入力されるとして、内部設定を行っています。

### 3.3. DC 特性

#### 3.3.1. 動作電源電流

表 3-5 動作電源電流

$V_{DD33} = 3.3 \text{ V}$ ,  $V_{SS} = 0.0 \text{ V}$ ,  $T_a = -40 \sim 85^\circ\text{C}$  出力端子開放

| 略号        | 条件                                                                          | 許容値 |     | 単位 |

|-----------|-----------------------------------------------------------------------------|-----|-----|----|

|           |                                                                             | typ | max |    |

| $I_{DD1}$ | $F_{OSC}=10 \text{ MHz}$ ,<br>PLL 使用,<br>内部クロック=最大周波数,<br>CPU 動作,<br>周辺回路動作 | 70  | 125 | mA |

#### 3.3.2. 入力端子 1 (Type-A)

TEST0(Pin#3)

表 3-6 入力端子 1 (Type-A)

$V_{DD33} = 3.3 \text{ V}$ ,  $V_{SS} = 0.0 \text{ V}$ ,  $T_a = -40 \sim 85^\circ\text{C}$

| 項目        | 略号        | 条件                                   | 許容値                   |     |                       | 単位            |

|-----------|-----------|--------------------------------------|-----------------------|-----|-----------------------|---------------|

|           |           |                                      | min                   | typ | max                   |               |

| 入力電圧ハイレベル | $V_{IH1}$ | $V_{DD33} = 3.0 \sim 3.6 \text{ V}$  | $V_{DD33} \times 0.7$ |     | $V_{DD33}$            | V             |

| 入力電圧ローレベル | $V_{IL1}$ | $V_{DD33} = 3.0 \sim 3.6 \text{ V}$  | $V_{SS}$              |     | $V_{DD33} \times 0.3$ |               |

| 入力リーク電流   | $I_{LK1}$ | $V_{IN} = 0 \sim V_{DD33} \text{ V}$ |                       |     | $\pm 5$               | $\mu\text{A}$ |

### 3.3.3. 入力端子2 (Type-B)

TEST1(Pin#12)、DbC(Pin#4)

表 3-7 入力端子2 (Type-B)

$V_{DD33} = 3.3 \text{ V}$ ,  $V_{SS} = 0.0 \text{ V}$ ,  $Ta = -40 \sim 85 \text{ }^{\circ}\text{C}$

| 項目        | 略号        | 条件                                  | 許容値                   |     |                       | 単位               |

|-----------|-----------|-------------------------------------|-----------------------|-----|-----------------------|------------------|

|           |           |                                     | min                   | typ | max                   |                  |

| 入力電圧ハイレベル | $V_{IH2}$ | $V_{DD33} = 3.0 \sim 3.6 \text{ V}$ | $V_{DD33} \times 0.7$ |     | $V_{DD33}$            | $\text{V}$       |

| 入力電圧ローレベル | $V_{IL2}$ | $V_{DD33} = 3.0 \sim 3.6 \text{ V}$ | $V_{SS}$              |     | $V_{DD33} \times 0.3$ |                  |

| 内蔵プルアップ抵抗 | $R_{I02}$ | $V_{IN} = 0 \text{ V}$              | 15                    | 30  | 60                    | $\text{k}\Omega$ |

### 3.3.4. 入力端子3 (Type-C)

nDin0(Pin#29)、nDin1(Pin#30)、nDin2(Pin#31)、nDin3(Pin#32)

表 3-8 入力端子3 (Type-C)

$V_{DD33} = 3.3 \text{ V}$ ,  $V_{SS} = 0.0 \text{ V}$ ,  $Ta = -40 \sim 85 \text{ }^{\circ}\text{C}$

| 項目        | 略号        | 条件                                   | 許容値                   |     |                       | 単位            |

|-----------|-----------|--------------------------------------|-----------------------|-----|-----------------------|---------------|

|           |           |                                      | min                   | typ | max                   |               |

| 入力電圧ハイレベル | $V_{IH3}$ | $V_{DD33} = 3.0 \sim 3.6 \text{ V}$  | $V_{DD33} \times 0.7$ |     | $V_{DD33}$            | $\text{V}$    |

| 入力電圧ローレベル | $V_{IL3}$ | $V_{DD33} = 3.0 \sim 3.6 \text{ V}$  | $V_{SS}$              |     | $V_{DD33} \times 0.3$ |               |

| 入力リーク電流   | $I_{LK3}$ | $V_{IN} = 0 \sim V_{DD33} \text{ V}$ |                       |     | $\pm 10$              | $\mu\text{A}$ |

### 3.3.5. 入出力端子1 (Type-D)

nRESET(Pin#2)

表 3-9 入出力端子1 (Type-D)

$V_{DD33} = 3.3 \text{ V}$ ,  $V_{SS} = 0.0 \text{ V}$ ,  $Ta = -40 \sim 85 \text{ }^{\circ}\text{C}$

| 項目        | 略号        | 条件                                                            | 許容値                   |     |                       | 単位               |

|-----------|-----------|---------------------------------------------------------------|-----------------------|-----|-----------------------|------------------|

|           |           |                                                               | min                   | typ | max                   |                  |

| 入力電圧ハイレベル | $V_{IH4}$ | $V_{DD33} = 3.0 \sim 3.6 \text{ V}$                           | $V_{DD33} \times 0.7$ |     | $V_{DD33}$            | $\text{V}$       |

| 入力電圧ローレベル | $V_{IL4}$ | $V_{DD33} = 3.0 \sim 3.6 \text{ V}$                           | $V_{SS}$              |     | $V_{DD33} \times 0.3$ |                  |

| 内蔵プルアップ抵抗 | $R_{I04}$ | $V_{IN} = 0 \text{ V}$                                        | 15                    | 30  | 60                    | $\text{k}\Omega$ |

| 出力電圧ローレベル | $V_{OL4}$ | $V_{DD33} = V_{RST33} \text{ V}$<br>$I_{OL} = 2.0 \text{ mA}$ |                       |     | 0.5                   | $\text{V}$       |

### 3.3.6. 入出力端子2 (Type-E)

DbD(Pin#5)

表 3-10 入出力端子2 (Type-E)

$V_{DD33} = 3.3 \text{ V}$ ,  $V_{SS} = 0.0 \text{ V}$ ,  $Ta = -40 \sim 85 \text{ }^{\circ}\text{C}$

| 項目        | 略号        | 条件                                  | 許容値                   |     |                       | 単位               |

|-----------|-----------|-------------------------------------|-----------------------|-----|-----------------------|------------------|

|           |           |                                     | min                   | typ | max                   |                  |

| 入力電圧ハイレベル | $V_{IH5}$ | $V_{DD33} = 3.0 \sim 3.6 \text{ V}$ | $V_{DD33} \times 0.7$ |     | $V_{DD33}$            | $\text{V}$       |

| 入力電圧ローレベル | $V_{IL5}$ | $V_{DD33} = 3.0 \sim 3.6 \text{ V}$ | $V_{SS}$              |     | $V_{DD33} \times 0.3$ |                  |

| 内蔵プルアップ抵抗 | $R_{IO5}$ | $V_{IN} = 0 \text{ V}$              | 15                    | 30  | 60                    | $\text{k}\Omega$ |

| 出力電圧ハイレベル | $V_{OH5}$ | $I_{OL} = -4.0 \text{ mA}$          | 2.8                   |     |                       | $\text{V}$       |

| 出力電圧ローレベル | $V_{OL5}$ | $I_{OL} = 4.0 \text{ mA}$           |                       |     | 0.5                   |                  |

### 3.3.7. 入出力端子3 (Type-F)

nSPICS(Pin#39)、SPICLK(Pin#40)、SPID(0)(Pin#41)、SPID(1)(Pin#42)、SPID(2)(Pin#43)、SPID(3)(Pin#44)

MODE(Pin#27)、RxD(Pin#21)

Reserved(Pin#1)、Reserved(Pin#14)、Reserved(Pin#23)、Reserved(Pin#28)

Reserved(Pin#33)、Reserved(Pin#34)、Reserved(Pin#46)、Reserved(Pin#47)、Reserved(Pin#48)

表 3-11 入出力端子3 (Type-F)

$V_{DD33} = 3.3 \text{ V}$ ,  $V_{SS} = 0.0 \text{ V}$ ,  $Ta = -40 \sim 85 \text{ }^{\circ}\text{C}$

| 項目        | 略号        | 条件                                   | 許容値                   |     |                       | 単位               |

|-----------|-----------|--------------------------------------|-----------------------|-----|-----------------------|------------------|

|           |           |                                      | min                   | typ | max                   |                  |

| 入力電圧ハイレベル | $V_{IH7}$ | $V_{DD33} = 3.0 \sim 3.6 \text{ V}$  | $V_{DD33} \times 0.7$ |     | $V_{DD33}$            | $\text{V}$       |

| 入力電圧ローレベル | $V_{IL7}$ | $V_{DD33} = 3.0 \sim 3.6 \text{ V}$  | $V_{SS}$              |     | $V_{DD33} \times 0.3$ |                  |

| 入力リーク電流   | $I_{LK7}$ | $V_{IN} = 0 \sim V_{DD33} \text{ V}$ |                       |     | $\pm 5$               | $\mu\text{A}$    |

| 内蔵プルアップ抵抗 | $R_{IO7}$ | $V_{IN} = 0 \text{ V}$               | 15                    | 30  | 60                    | $\text{k}\Omega$ |

| 出力電圧ハイレベル | $V_{OH7}$ | $I_{OL} = -4.0 \text{ mA}$           | 2.8                   |     |                       | $\text{V}$       |

| 出力電圧ローレベル | $V_{OL7}$ | $I_{OL} = 4.0 \text{ mA}$            |                       |     | 0.5                   |                  |

### 3.3.8. 出力端子1 (Type-G)

nINT(Pin#26)、nPF(Pin#45)、TxE(Pin#35)、TxD(Pin#15)、nMON(Pin#36)、nLCARE(Pin#37)、nMCARE(Pin#38)

nDout0(Pin#16)、nDout1(Pin#17)、nDout2(Pin#18)、nDout3(Pin#19)

$V_{DD33} = 3.3 \text{ V}$ ,  $V_{SS} = 0.0 \text{ V}$ ,  $T_a = -40 \sim 85 \text{ }^{\circ}\text{C}$

表 3-12 出力端子1 (Type-G)

| 項目        | 略号        | 条件                         | 許容値 |     |     | 単位 |

|-----------|-----------|----------------------------|-----|-----|-----|----|

|           |           |                            | min | typ | max |    |

| 出力電圧ハイレベル | $V_{OH7}$ | $I_{OL} = -4.0 \text{ mA}$ | 2.8 |     |     |    |

| 出力電圧ローレベル | $V_{OL7}$ | $I_{OL} = 4.0 \text{ mA}$  |     |     | 0.5 | V  |

## 3.4. アナログ特性

### 3.4.1. 内部発振

表 3-13 アナログ特性:内部発振

$V_{DD33} = V_{RST33N} \sim 3.6 \text{ V}$ ,  $V_{SS} = 0.0 \text{ V}$ ,  $T_a = -40 \sim 85 \text{ }^{\circ}\text{C}$

| 項目    | 略号       | 条件 | 許容値 |     |     | 単位  |

|-------|----------|----|-----|-----|-----|-----|

|       |          |    | min | typ | max |     |

| 発振周波数 | $F_{RC}$ |    | 9   | 10  | 11  | MHz |

### 3.4.2. パワーオンリセット

表 3-14 アナログ特性:リセット

$V_{SS} = 0.0 \text{ V}$ ,  $T_a = -40 \sim 85 \text{ }^{\circ}\text{C}$

| 項目        | 略号                 | 条件   | 許容値  |      |      | 単位   |

|-----------|--------------------|------|------|------|------|------|

|           |                    |      | min  | typ  | max  |      |

| 電源電圧検知レベル | $V_{RST33P}$       | 立上り時 | 2.90 | 2.95 | 3.00 | V    |

|           | $V_{RST33N}$       | 立下り時 | 2.80 | 2.85 | 2.90 |      |

| 電源電圧変化率   | $\Delta V_{DD33P}$ | 立上り時 | 0.5  |      | 5    | V/ms |

|           | $\Delta V_{DD33N}$ | 立下り時 |      |      | 1    |      |

電源投入時の立上り時間が min の数値より遅い場合、内部の初期化時間が長くなり、リセット端子から L<sub>0</sub> レベルを出し続けます。外部のリセット回路および制御ソフトはこの点を考慮して設計してください。

図 3-3 リセットタイミング

### 3.5. AC 特性

#### 3.5.1. リセット

表 3-15 AC 特性:リセット

$V_{DD33} = V_{RST33N} \sim 3.6 \text{ V}$ ,  $V_{SS} = 0.0 \text{ V}$ ,  $T_a = -40 \sim 85 \text{ }^\circ\text{C}$

| 項目                       | 略号          | 条件 | 許容値 |     |     | 単位            |

|--------------------------|-------------|----|-----|-----|-----|---------------|

|                          |             |    | min | typ | max |               |

| パワーオンリセット後<br>Lo レベル出力時間 | $t_{NRSTW}$ |    | 1   |     |     | $\mu\text{s}$ |

「図 1-5 電源投入時の電圧推移」で説明の通り、電源電圧の立ち上り時間により、リセット出力時間は変化します。外部のリセット回路はこの時間を考慮して設計してください。

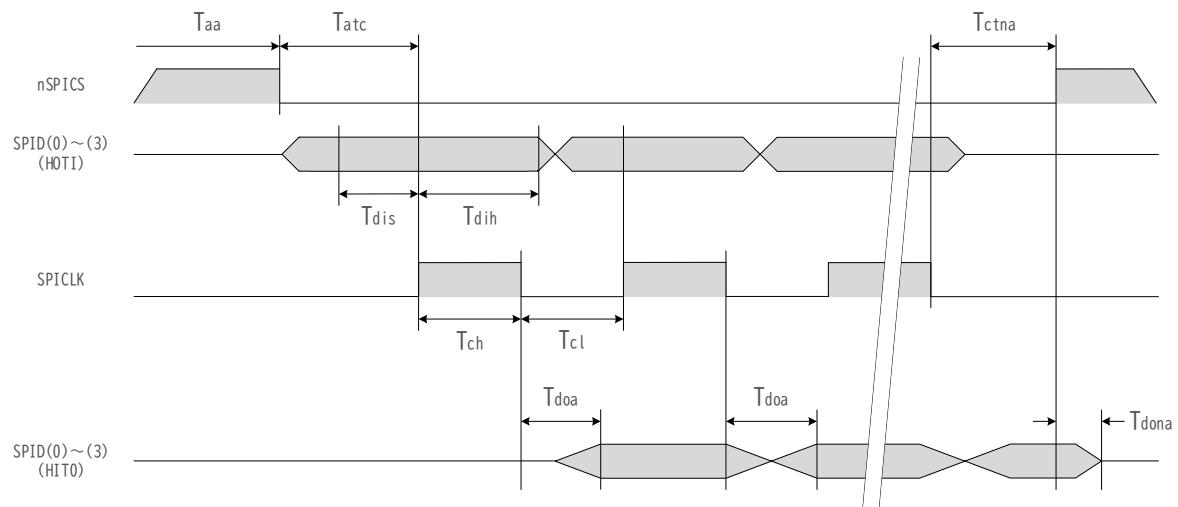

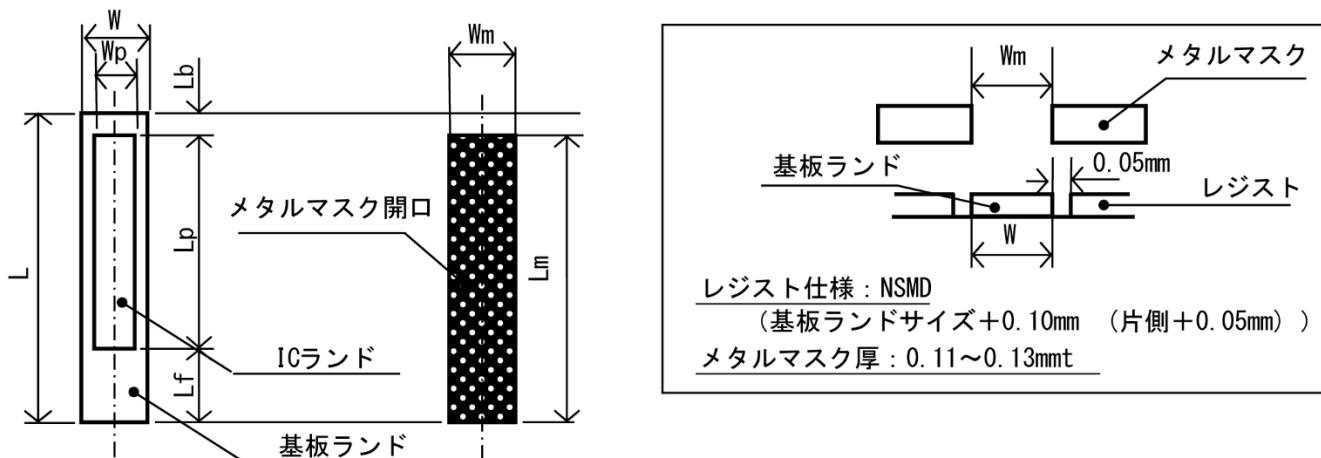

### 3.5.2. SPI インターフェイス

図 3-4 SPI インターフェイス

表 3-16 AC 特性:SPI インターフェイス

内部動作クロック (M-CLK) は 120MHz のため、1 M-CLK = 8.33nsec

| 項目            | 略号    | 許容値     |     |     | 単位 |

|---------------|-------|---------|-----|-----|----|

|               |       | min     | typ | max |    |

| アクセス終了～開始     | Taa   | 4×M-CLK |     |     | ns |

| アクセス開始～クロック   | Tatc  | 2×M-CLK |     |     |    |

| クロック～アクセス終了   | Tctna | 2×M-CLK |     |     |    |

| 入力データセットアップ   | Tdis  | 10      |     |     |    |

| 入力データホールド     | Tdih  | 10      |     |     |    |

| クロック Hi 期間    | Tch   | 30      |     |     |    |

| クロック Lo 期間    | Tcl   | 30      |     |     |    |

| Hi-Z ~出力データ確定 | Tdoa  |         |     | 30  |    |

| 出力データ確定～Hi-Z  | Tdona |         |     | 10  |    |

### 3.5.3. 転送レートタイミング

図 3-5 転送タイミング

表 3-17 AC 特性:データ転送タイミング

| 項目         | 略号        | 許容値                   |                      |                       | 単位 |

|------------|-----------|-----------------------|----------------------|-----------------------|----|

|            |           | min                   | typ                  | max                   |    |

| 入力信号 短パルス幅 | $T_{RNW}$ | $0.51 \times T_{BPS}$ | $1.0 \times T_{BPS}$ | $1.49 \times T_{BPS}$ | ns |

| 入力信号 長パルス幅 | $T_{RWW}$ | $1.76 \times T_{BPS}$ | $2.0 \times T_{BPS}$ | $2.24 \times T_{BPS}$ |    |

$T_{BPS}$  は転送レートによって変化する。

表 3-18 転送レートと  $T_{BPS}$

| 略号        | 転送レート   | 許容値        |        |            | 単位 |

|-----------|---------|------------|--------|------------|----|

|           |         | min        | typ    | max        |    |

| $T_{BPS}$ | 12 Mbps | 83.33 - 5  | 83.33  | 83.33 + 5  | ns |

|           | 6 Mbps  | 166.67 - 5 | 166.67 | 166.67 + 5 |    |

|           | 3 Mbps  | 333.33 - 5 | 333.33 | 333.33 + 5 |    |

## 4. 付録

### 4.1. パッケージ外形寸法

図 4-1 外形寸法図

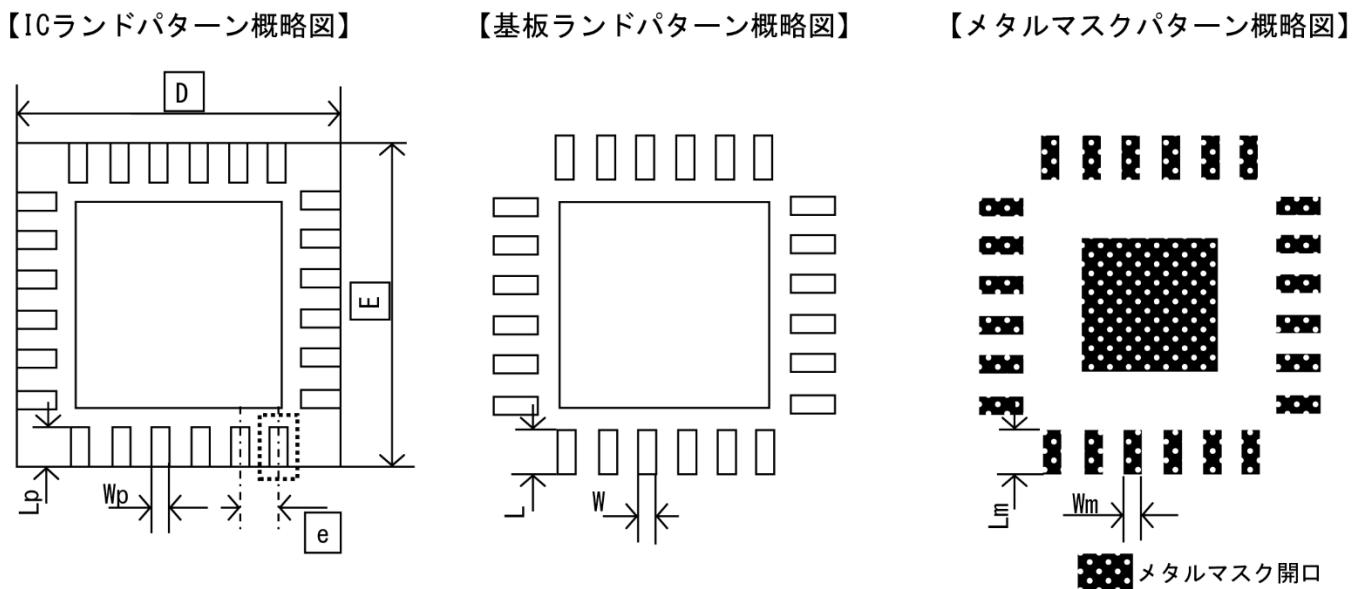

## 4.2. QFN用参考基板ランド図

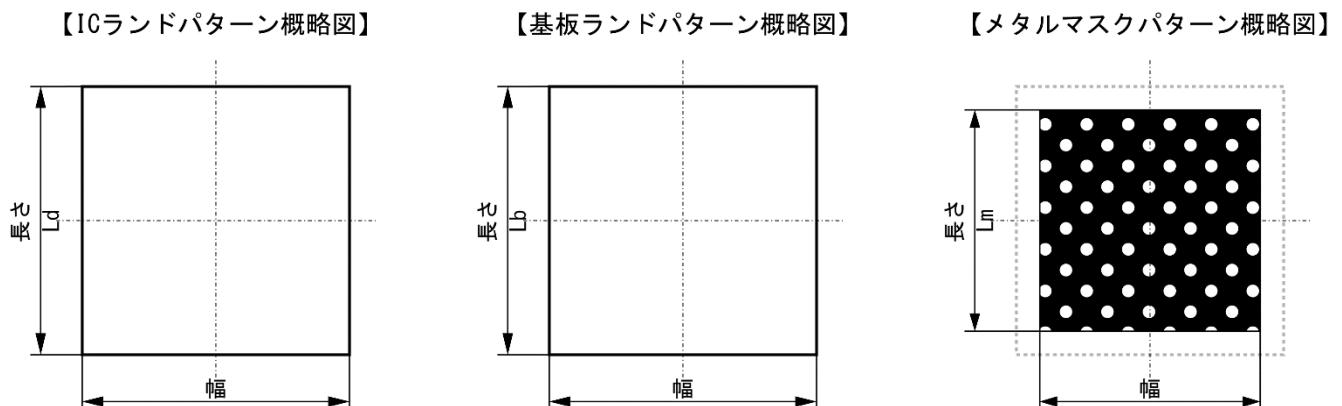

【ICランドー基板ランドーメタルマスク配置】

図 4-2 推奨ランドパターン

表 4-1 パターンサイズ

|        | 記号 | 名称      | 数値   |  | 記号 | 名称        | 数値   |

|--------|----|---------|------|--|----|-----------|------|

| パッケージ  | D  | パッケージ長さ | 7.0  |  | W  | 基板ランド幅    | 0.26 |

|        | E  | パッケージ幅  | 7.0  |  | L  | 基板ランド長さ   | 0.55 |

|        | e  | 端子ピッチ   | 0.50 |  | Lf | フロントフィレット | 0.10 |

|        | Wp | リード幅    | 0.25 |  | Lb | バックフィレット  | 0.05 |

|        | Lp | リード長さ   | 0.4  |  | Wm | メタルマスク幅   | 0.26 |

| 単位: mm |    |         |      |  | Lm | メタルマスク長さ  | 0.50 |

上記の数値は参考値であり、実際の実装条件・環境による実装評価を実施してください。

放熱用ダイパッドの設計寸法は下記にもとづき基板設計をお願いします。

図 4-3 推奨放熱パッド

#### 【放熱ランド部の寸法の考え方】

パッケージダイパット部：幅  $W_d = 5.15\text{mm}$ 、長さ  $L_d = 5.15\text{mm}$

基板ランドダイパット部：幅  $W_b = W_d = 5.15\text{mm}$ 、長さ  $L_b = L_d = 5.15\text{mm}$

メタルマスク開口：基板ランド面積比が 50~70%となるよう 幅  $W_m$ 、長さ  $L_m$  を決める

$$(W_m \times L_m) \div (W_b \times L_b) \approx 50\sim70\%$$

上記の通りプリント基板上の Cu ランドパターンは、デバイス中央に露出したパッケージダイパット放熱部と同一形状とし、メタルマスク開口寸法は Cu ランドパターンよりも小さくすることをお奨めします。

メタルマスク開口を Cu ランドパターンよりも大きくした場合、レジスト上のはんだ浮遊によるキャピラリーボールやはんだブリッジなどのはんだ不良を引き起こす恐れがあります。

#### 【放熱部の実装上の注意事項】

実際の実装条件・環境により、はんだ不良（ボイド・ブリッジ）が発生することがあります。

必ず実装評価を実施し、(QFN パッケージは外観検査で判定が難しいため) X 線観察などで実装状態を確認されることを推奨します。

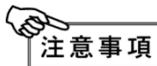

### 4.3. 実装推奨条件

デバイスにおける実装時の耐熱限界を示します。

実装信頼性を保証するものではありません。

実装条件は、ご使用されるはんだ材等の材料に合った適切な条件を設定してください。

リフロー：本プロファイルは、温風リフロー・赤外線リフロー等に適用する

リフローピーク温度 : 最大 260 °C

リフロー回数 : 2 回以内

図 4-4 温度プロファイルカーブ

表 4-2 プロファイルパラメーター

| No | 記号 | 内容          | 値              |

|----|----|-------------|----------------|

| 1  | T1 | プリヒート温度     | 150°C~180°C    |

| 2  | t1 | プリヒート温度保持時間 | 60 s~120 s     |

| 3  | a  | 昇温レート       | 2°C/s~5°C/s    |

| 4  | Tp | ピーク温度       | 255°C+5°C、-0°C |

| 5  | tp | ピーク温度保持時間   | 10 s±3 s       |

| 6  | tw | 高温領域保持時間    | 220°C、60 s 以内  |

| 7  | b  | 冷却レート       | 2°C/s~5°C/s    |

| 8  | -  | リフロー回数      | 2 回以内          |

※温度は、デバイスの樹脂表面温度を示します

ピーク温度は 260°C を超えないよう制御してください。

➤ 改訂履歴

| Revision | 発行日        | 改訂内容 |

|----------|------------|------|

| 100      | 2025/08/08 | 新規作成 |

|          |            |      |

## ご注意

- 1) 本資料に記載された内容は、将来予告なしに変更する場合があります。本製品をご使用になる際には、本資料が最新の版であるかをご確認ください。

- 2) 本資料において記載されている説明や回路例などの技術情報は、お客様が用途に応じて本製品を適切にご利用いただくための参考資料です。

- 3) 実際に本製品をご使用になる際には、基板上における本製品の周辺回路条件や環境を考慮の上、お客様の責任においてシステム全体を十分に評価し、お客様の目的に適合するようシステムを設計してください。当社は、お客様のシステムと本製品との適合可否に対する責任を負いません。

- 4) 本資料に記載された情報、製品および回路等の使用に起因する損害または特許権その他権利の侵害に関して、当社は一切その責任を負いません。

- 5) 本製品および本資料の情報や回路などをご使用になる際、当社は第三者の工業所有権、知的所有権およびその他権利に対する保証または実施権を許諾致しません。

- 6) 本製品は、人命に関わる装置用としては開発されておりません。人命に関わる用途への採用をご検討の際は、当社までご相談ください。

- 7) 本資料の一部または全部を、当社に無断で転載および複製することを禁じます。

## ➤ お問い合わせ先

株式会社ステップテクニカ

〒207-0021 東京都東大和市立野一丁目1番地の15

E-Mail: info@steptechnica.com