STD\_CU40\_V2.7E

STEP ECHNICA CO., LTD.

CUnet CUnet IC MKY40

User's Manual

### **Note**

- 1. The information in this document is subject to change without prior notice. Before using this product, please confirm that this is the latest version of this document.

- 2. Technical information in this document, such as explanations and circuit examples, are references for this product. When actually using this product, always fully evaluate the entire system according to the design purpose based on considerations of peripheral circuits and the PC board environment. We assume no responsibility for any incompatibility between this product and your system.

- 3. We assume no responsibility whatsoever for any losses or damages arising from the use of the information, products, and circuits in this document, or for infringement of patents and any other rights of a third party.

- 4. When using this product and the information and circuits in this document, we do not guarantee the right to use any property rights, intellectual property rights, and any other rights of a third party.

- 5. This product is not designed for use in critical applications, such as life support systems. Contact us when considering such applications.

- 6. No part of this document may be copied or reproduced in any form or by any means without prior written permission from StepTechnica Co., Ltd.

### **Preface**

This manual describes the MKY40, or a kind of CUnet IC.

Be sure to read "CUnet Introduction Guide" before understanding this manual and the MKY40.

### Target Readers

This manual is for:

- Those who first build a CUnet

- Those who first use StepTechnica's various ICs to build a CUnet

### Prerequisites

This manual assumes that you are familiar with:

- Network technology

- Semiconductor products (especially microcontrollers and memory)

#### Related Manuals

- CUnet Introduction Guide

- CUnet Technical Guide

### [Caution]

- To users with "CUnet User's Manual" released before March, 2001

Some terms in this manual have been changed to conform to International Standards.

- Some terms in this manual are different from those used on our website and in our product brochures. The brochure uses ordinary terms to help many people in various industries understand our products.

Please understand technical information on HLS Family and CUnet Family based on technical documents (manuals).

# **CONTENTS**

| C | hapt | er 1 | MKY40 Role and Features                           |       |

|---|------|------|---------------------------------------------------|-------|

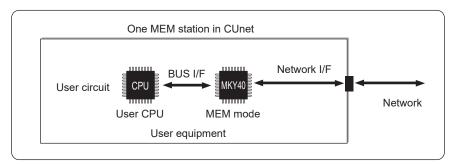

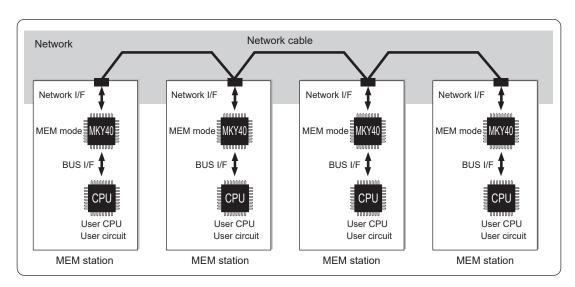

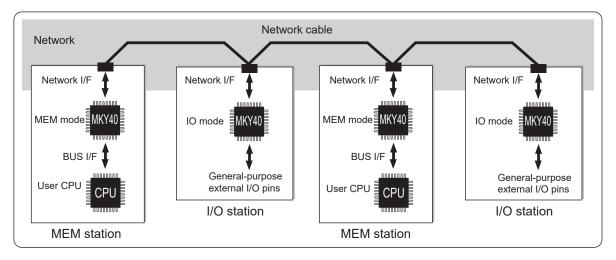

|   | 1.1  | CU   | net Station in MEM Mode (MEM Station)             | 1-3   |

|   | 1.2  | Fea  | atures of MEM Mode                                | 1-4   |

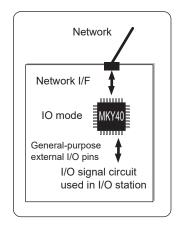

|   | 1.3  | Sta  | tion in IO Mode (I/O Station)                     | 1-5   |

|   | 1.4  | Fea  | atures of IO Mode                                 | 1-6   |

|   | 1.5  | Мо   | de Selection                                      | 1-6   |

|   |      |      |                                                   |       |

| С | hapt | er 2 | Hardware in MEM Mode                              | . 2-3 |

|   |      |      |                                                   |       |

| С | hapt | er 3 | Connections in MEM Mode                           |       |

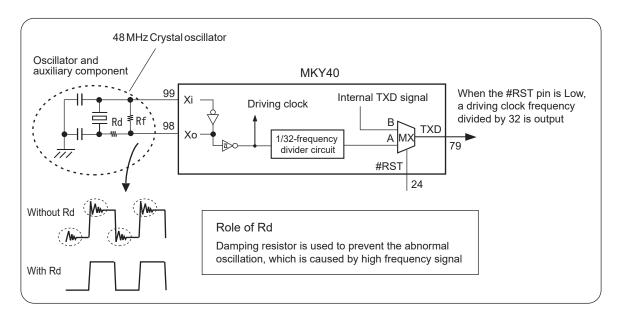

|   | 3.1  | Dri  | ving Clock                                        | 3-4   |

|   | 3.   | 1.1  | Self-generation of Driving Clock                  | 3-4   |

|   | 3.   | 1.2  | Supplying Generated Driving Clock                 | 3-5   |

|   | 3.   | 1.3  | Checking Driving Clock                            | 3-5   |

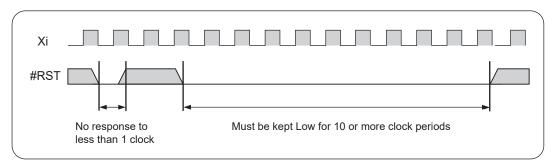

|   | 3.2  | Har  | rdware Reset                                      | 3-6   |

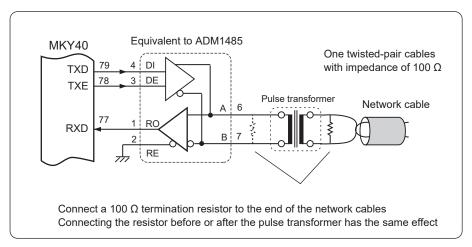

|   | 3.3  | Coi  | nnecting Network Interface                        | 3-7   |

|   | 3.   | 3.1  | Recommended Network Connection                    | 3-7   |

|   | 3.   | 3.2  | Details of RXD, TXE, and TXD Pins                 |       |

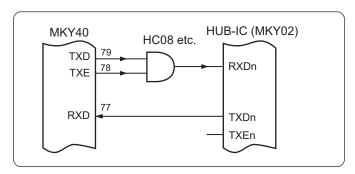

|   | 3.   | 3.3  | Cautions for Directly-Connecting to HUB-IC        |       |

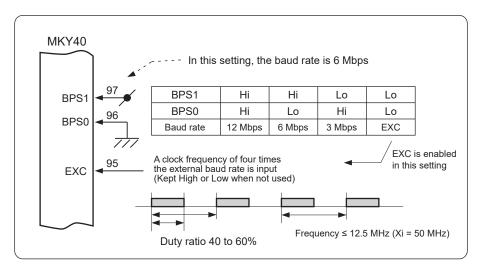

|   | 3.4  | Set  | ting Baud Rate                                    | 3-9   |

|   | 3.5  | Net  | work Cable Length                                 | .3-10 |

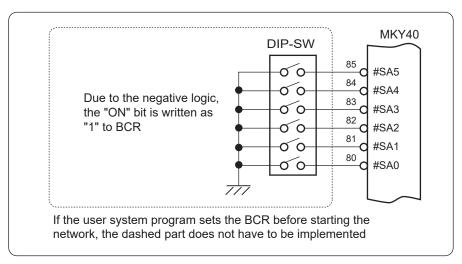

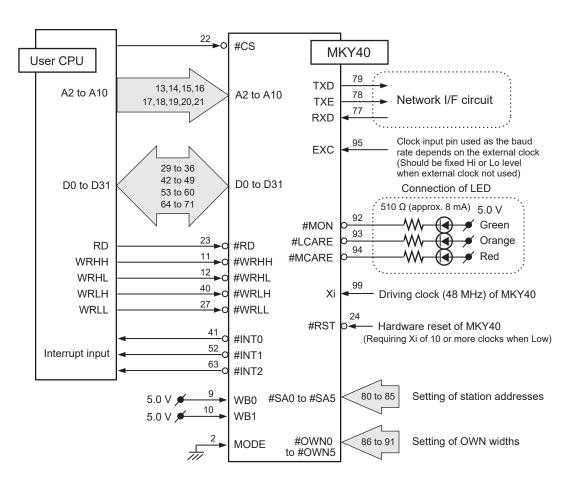

|   | 3.6  | Set  | ting Station Addresses                            | .3-11 |

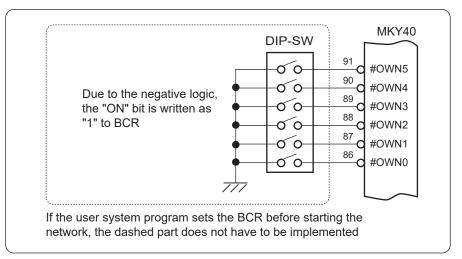

|   | 3.7  | Exp  | oansion Setting for Owned Area                    | .3-12 |

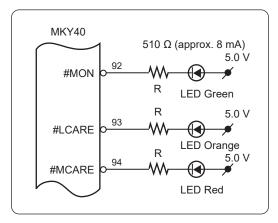

|   | 3.8  | Coi  | nnecting LED Indication Pins                      | .3-13 |

|   | 3.9  | Coi  | nnection of Timing Notification Signal (#STB Pin) | .3-14 |

|   | 3.10 | Coi  | nnecting PING Signal                              | .3-14 |

|   | 3.11 | Coi  | nnecting General-purpose Output Ports             | .3-15 |

|   | 3.12 |      | nnecting User CPU                                 |       |

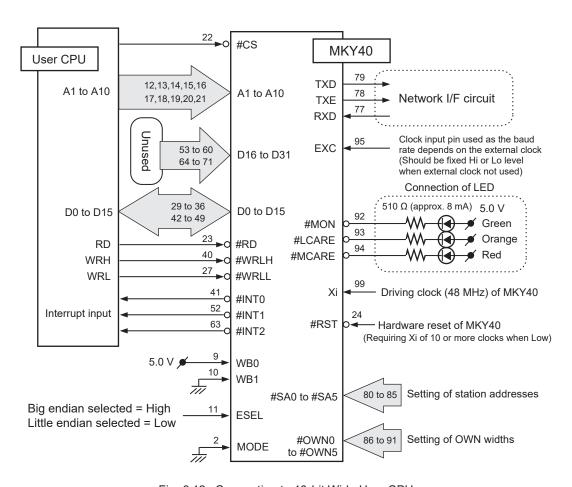

|   |      | 12.1 | Connection of 32-bit Wide User CPU                |       |

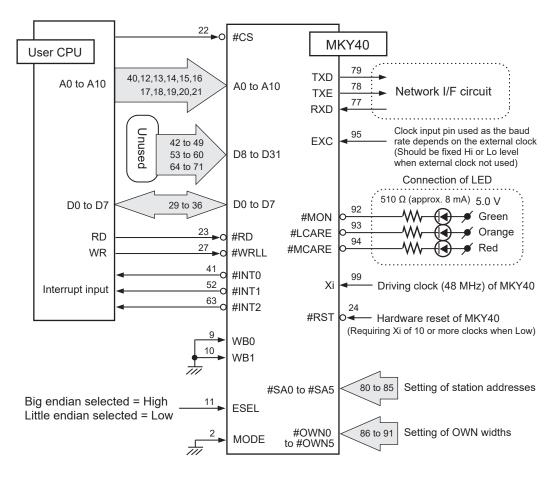

|   | 3.   | 12.2 | Connection of 16-bit Wide User CPU                | .3-18 |

|   | 3.   | 12.3 | Connection of 8-bit Wide User CPU                 | 3-20  |

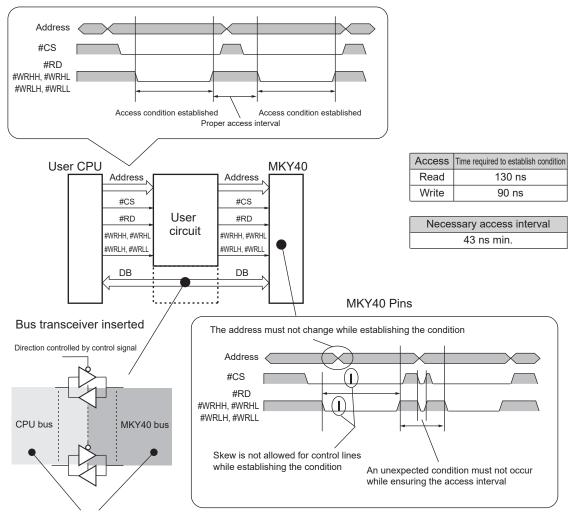

|   | 3.   | 12.4 | Recognition of Access                             | .3-21 |

|   | 3.   | 12.5 | Designing Access Time                             | 3-22  |

|   | 3.   | 12.6 | Access Test after Embedding MKY40                 |       |

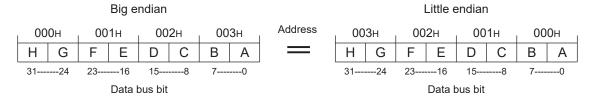

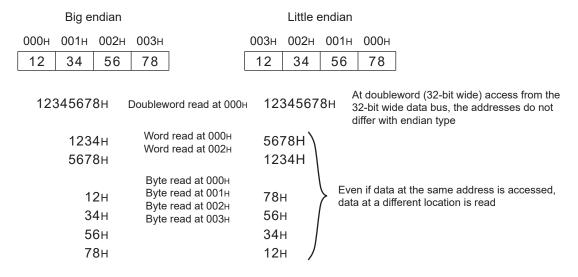

|   |      | 12.7 | Data Storage Method                               |       |

|   | 3.   | 12.8 | Connection of Interrupt Trigger Signals           | 3-24  |

## **Chapter 4** Software in MEM Mode

| 4.1 | Sta   | art and Stop of Communication                           | 4-3  |

|-----|-------|---------------------------------------------------------|------|

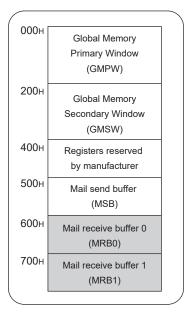

| 4.1 | l.1   | Memory Map                                              | 4-4  |

| 4.1 | 1.2   | Checking Connection of MKY40                            | 4-4  |

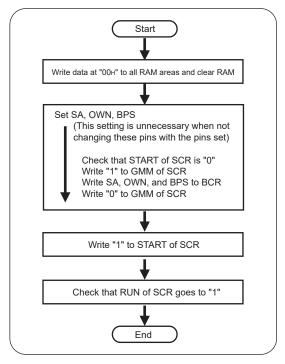

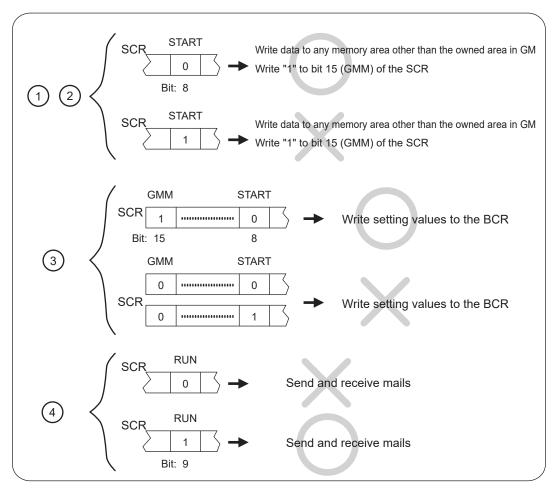

| 4.1 | 1.3   | Initialization and Start-up of Communication            | 4-5  |

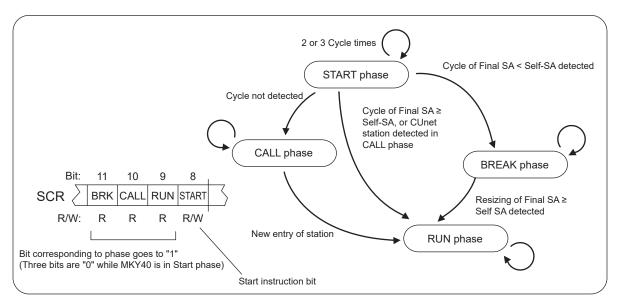

| 4.1 | 1.4   | Responses to Each Phase                                 | 4-6  |

| 4.1 | 1.5   | Protection against Misoperation                         | 4-7  |

| 4.1 | 1.6   | Cycle Time of CUnet                                     |      |

| 4.1 | 1.7   | Detailed Timing during Cycle                            |      |

| 4.1 | 1.8   | Network Stop                                            |      |

|     | 4.1.8 | •                                                       |      |

|     | 4.1.8 | •                                                       |      |

|     | 4.1.8 | 8.3 Stop Exception 1                                    | 4-10 |

|     | 4.1.8 | 8.4 Stop Exception 2                                    | 4-11 |

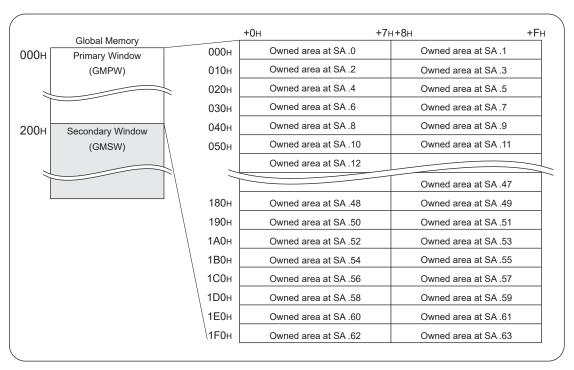

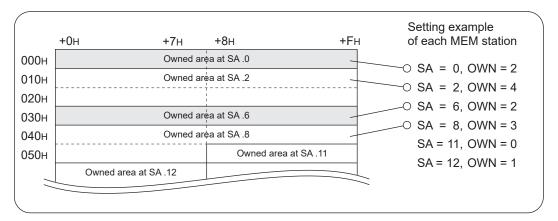

| 4.2 | Use   | e of GM                                                 | 4-12 |

| 4.2 | 2.1   | Details of Owned Area                                   | 4-12 |

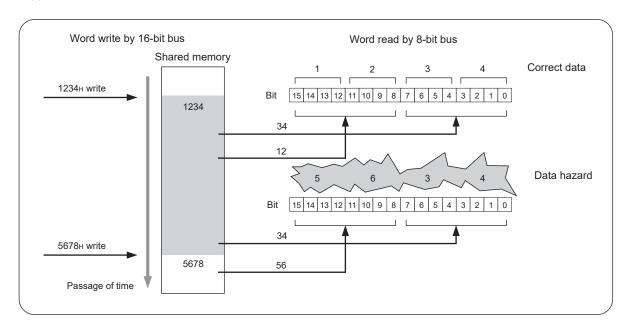

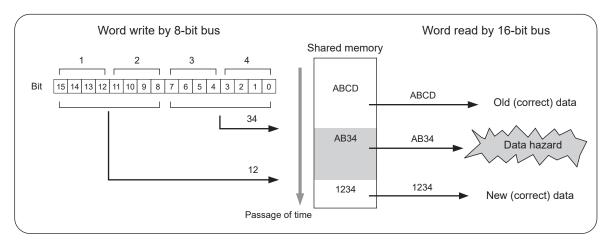

| 4.2 | 2.2   | Data Hazards and Protection Against Data Hazards        |      |

|     | 4.2.  | .2.1 Window Lock                                        |      |

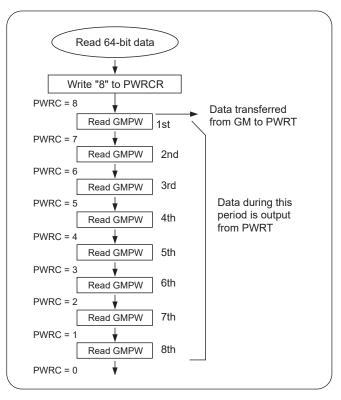

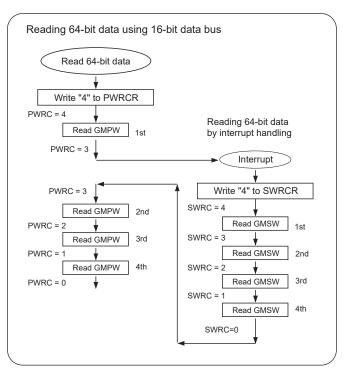

|     |       | .2.2 GMPW Read Window Lock                              |      |

|     | 4.2.2 | .2.3 GMPW Write Window Lock                             | 4-16 |

|     | 4.2.2 | .2.4 Relation between Window Lock Functions             | 4-17 |

|     | 4.2.2 | .2.5 Global Memory Secondary Window (GMSW)              | 4-17 |

|     | 4.2.2 | .2.6 Appropriate Use of GMPW and GMSW                   | 4-18 |

|     | 4.2.2 | .2.7 Protection Against Data Hazard Without Window I    |      |

| 4.2 | 2.3   | Quality Assurance of GM Data                            | 4-20 |

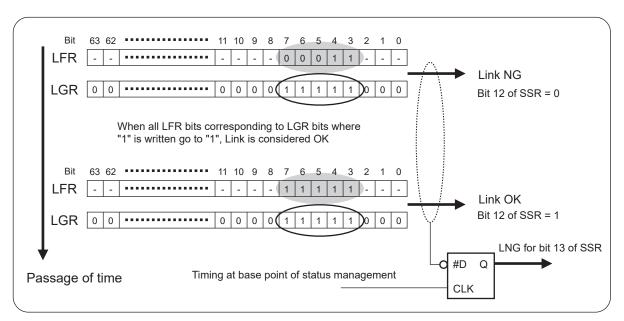

|     |       | .3.1 Status Indication by Registers                     |      |

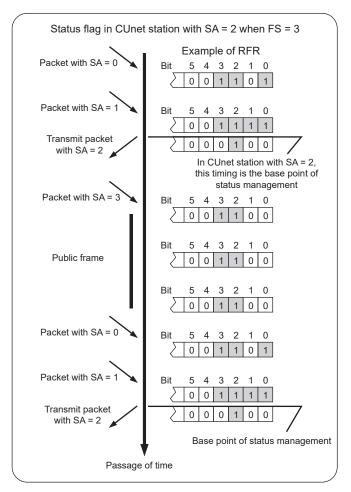

|     |       | .3.2 Starting Point of Status Management and Exception  |      |

|     |       | .3.3 Link Group Register (LGR)                          |      |

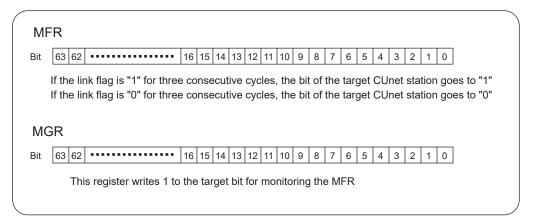

|     |       | .3.4 Member                                             |      |

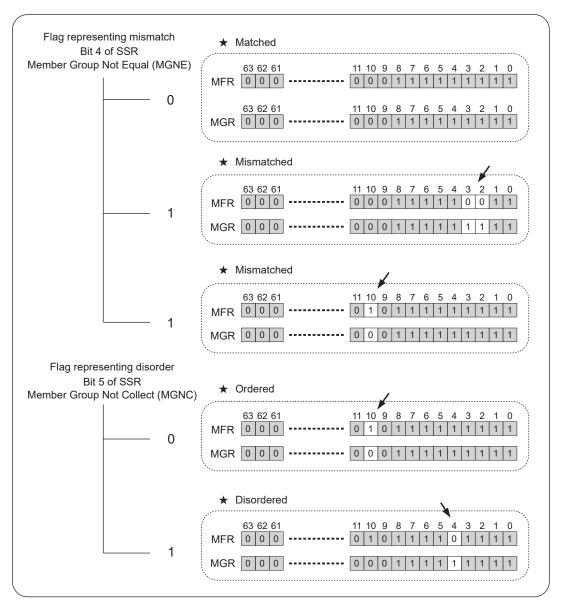

|     |       | .3.5 Member Flag Register (MFR)                         |      |

|     |       | .3.6 Member Group Register (MGR)                        |      |

|     |       |                                                         |      |

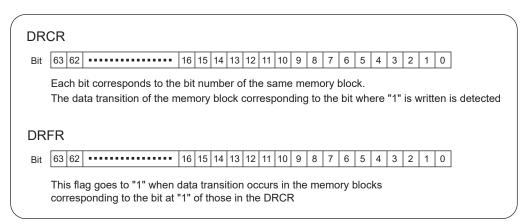

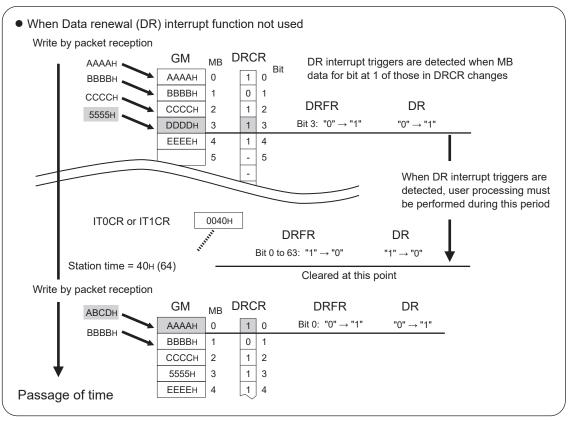

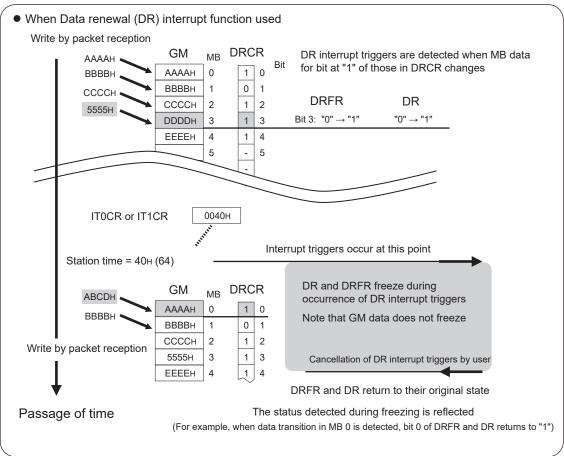

| 4.2 | 2.4   | Detection of Global Memory Data Transition              |      |

|     | 4.2.4 | .4.1 Data Renewal Check Register (DRCR) for Setting i   |      |

|     |       | .4.3 Transition Timing of DR Flag Bit and DRFR Bits fro |      |

|     |       | 4.4 Precautions for Use of Detection of Data Transitio  |      |

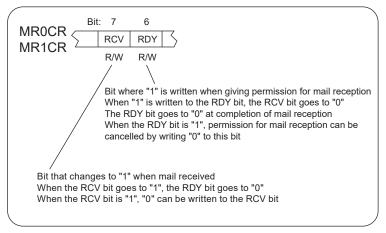

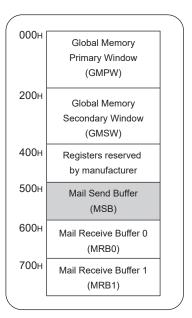

| 4.3 |       | e of Mail Sending/Reception Function                    |      |

|     |       | • •                                                     |      |

| 4.3 |       | Permission for Mail Reception                           |      |

|     | 3.2   | Operation for Mail Reception                            |      |

| 4.3 |       | Operation for Mail Sending and after Completion of So   | _    |

| 4.3 | 3.4   | Operation against Mail Sending Errors                   |      |

| 4.3 | 3.5   | Quality Assurance for Mail Sending/Reception            | 4-39 |

| 4.3 | 3.6   | User-support Functions in Mail Sending/Reception        | 4-39 |

| 4.3 | 3.7   | Estimation of Mail Sending/Reception Time               | 4-40 |

| 4.3 | 3.8   | Precautions for Mail Sending/Reception                  | 4-40 |

| 4.4    | Deta | alled Operation and Management of Cunet System                         | . 4-41 |

|--------|------|------------------------------------------------------------------------|--------|

| 4.4    | 4.1  | Monitoring before Network Start                                        | . 4-42 |

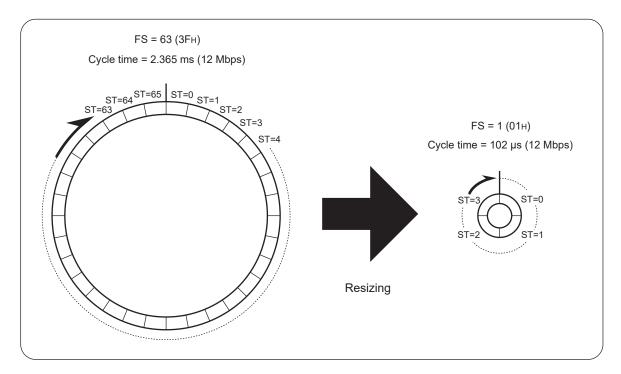

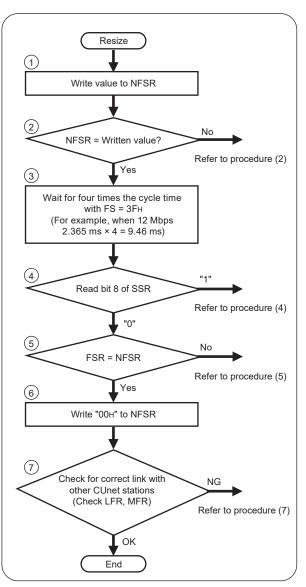

| 4.4    | 4.2  | Resizing of Cycle Time                                                 | . 4-43 |

|        |      | .1 Resizing                                                            |        |

|        |      | .2 Rejection of Resizing                                               |        |

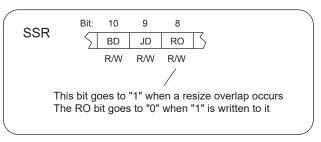

|        |      | .3 Resize Overlap (RO)                                                 |        |

|        |      | .4 Caution when RO Occurs                                              |        |

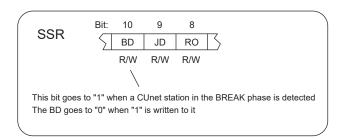

| 4.4    |      | Detection and Handling of CUnet Station in BREAK Phase                 |        |

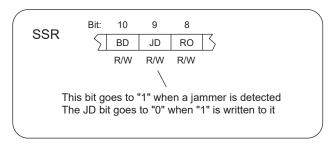

| 4.4    |      | Detection and Handling of Jammer                                       |        |

| 4.4    |      | Controling and Monitoring Network Quality                              |        |

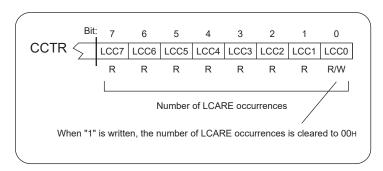

|        |      | .1 LCARE Signal Output                                                 |        |

|        |      | .2 MCARE Signal Output                                                 |        |

|        |      | .3 MON Signal Output                                                   |        |

|        |      | PING Instruction                                                       |        |

| 4.4    |      | Function to Detect Mode of Each Station                                |        |

| 4.4    |      | Operation of General-purpose Output Ports                              |        |

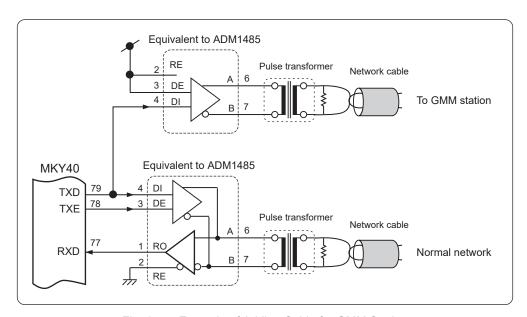

| 4.4    |      | Global Memory Monitor (GMM) Function                                   |        |

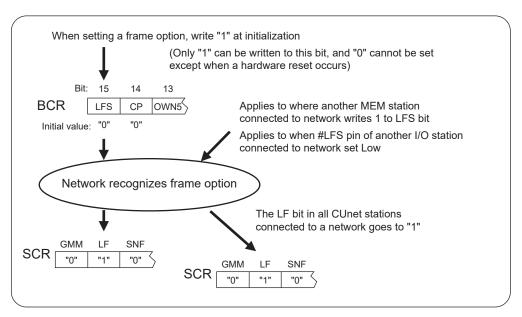

| 4.4    |      | Frame Option [for HUB]                                                 |        |

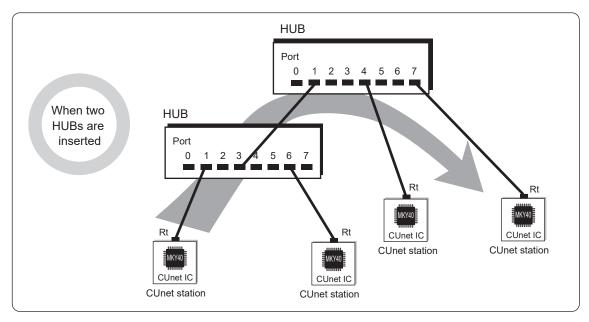

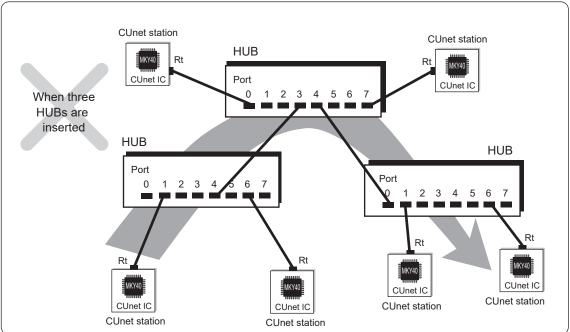

|        |      | 0.1 Number of Insertable HUBs                                          |        |

|        |      | 0.2 Setting of Frame Option                                            |        |

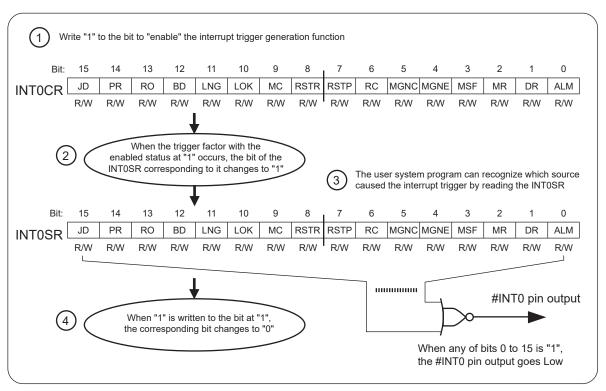

| 4.5    |      | rrupt Trigger Generation Function                                      |        |

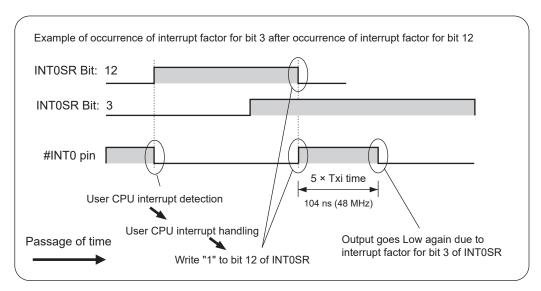

| 4.5    | 5.1  | Operation of #INT0 Pin                                                 | . 4-62 |

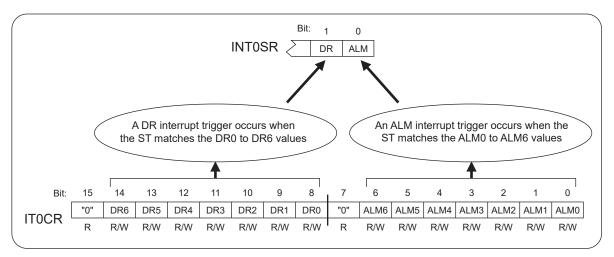

| 4.5    | 5.2  | Retrigger Function                                                     | . 4-64 |

| 4.5    | 5.3  | Interrupt Factors                                                      | . 4-65 |

| 4.5    | 5.4  | Operation of #INT1 Pin                                                 | . 4-66 |

| 4.5    | 5.5  | Operation of #INT2 Pin                                                 | . 4-66 |

| 4.5    | 5.6  | Precautions for Specifying Timing of Interrupt Trigger Generation      | . 4-66 |

| 4.5    | 5.7  | Precautions for Use of Data Renewal (DR) Interrupt Trigger             | . 4-67 |

| 4.5    | 5.8  | Register Freezing in Synchronization with Interrupt Trigger Generation | . 4-67 |

|        |      |                                                                        |        |

| Chapte | er 5 | Register Reference in MEM Mode                                         |        |

| 5.1    | Chip | Code Register (CCR)                                                    | 5-5    |

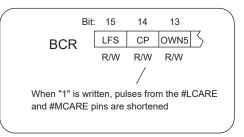

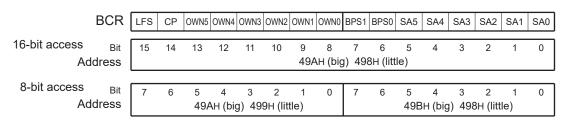

| 5.2    | Bas  | ic Control Register (BCR)                                              | 5-6    |

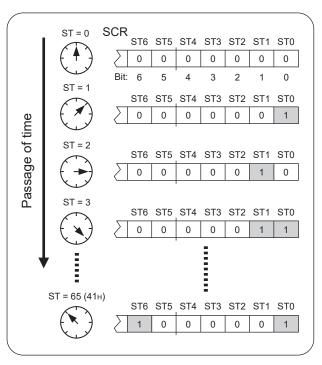

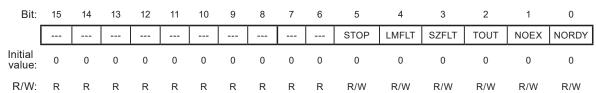

| 5.3    | Syst | tem Control Register (SCR)                                             | 5-8    |

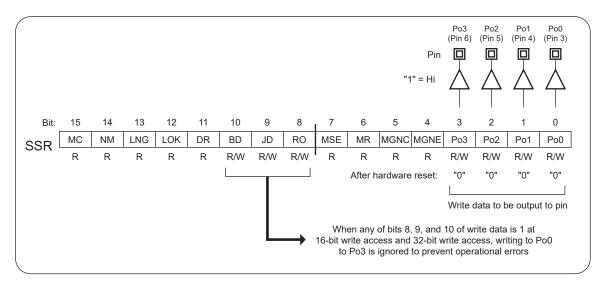

| 5.4    | Syst | tem Status Register (SSR)                                              | 5-10   |

| 5.5    | Fina | I Station Register (FSR)                                               | 5-12   |

| 5.6    |      | Final Station Register (NFSR)                                          |        |

| 5.7    |      | eive Flag Register (RFR)                                               |        |

| 5.8    |      | Flag Register (LFR)                                                    |        |

| 5.9    |      |                                                                        |        |

|        |      | Group Register (LGR)                                                   |        |

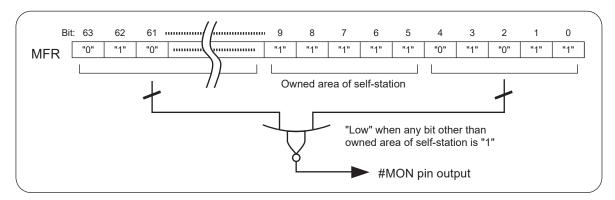

| 5.10   |      | nber Flag Register (MFR)                                               |        |

| 5.11   | Men  | nber Group Register (MGR)                                              | 5-17   |

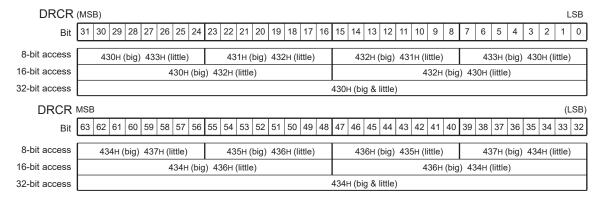

| 5.12   | Data Renewal Check Register (DRCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .5-18  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 5.13   | Data Renewal Flag Register (DRFR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .5-19  |

| 5.14   | Primary Window Read Control Register (PWRCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-20   |

| 5.15   | Primary Window Write Control Register (PWWCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-20   |

| 5.16   | Secondary Window Read Control Register (SWRCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-21   |

| 5.17   | Secondary Window Write Control Register (SWWCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-21   |

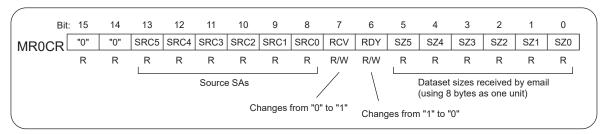

| 5.18   | Mail Receive 0 Control Register (MR0CR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |

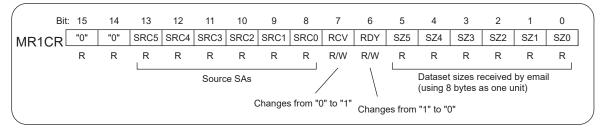

| 5.19   | Mail Receive 1 Control Register (MR1CR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-23   |

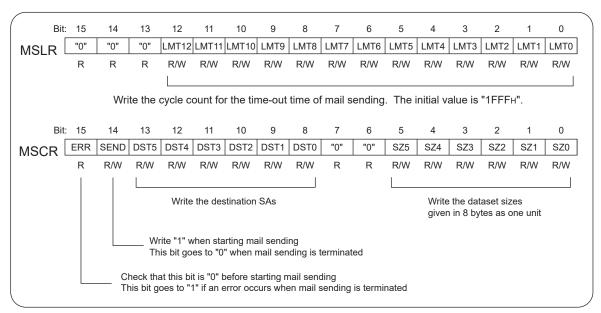

| 5.20   | Mail Send Control Register (MSCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-24   |

| 5.21   | Mail Send Limit time Register (MSLR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-25   |

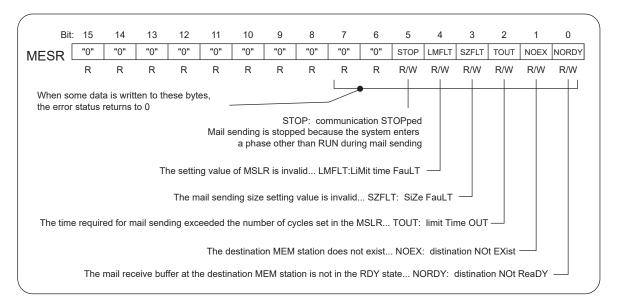

| 5.22   | Mail Error Status Register (MESR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-26   |

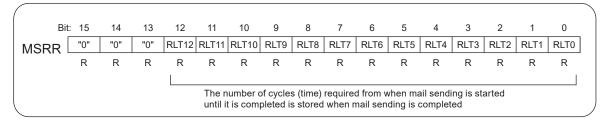

| 5.23   | Mail Send Result Register (MSRR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-27   |

| 5.24   | INTerrupt 0 Control Register (INT0CR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-28   |

| 5.25   | INTerrupt 1 Control Register (INT1CR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-30   |

| 5.26   | INTerrupt 2 Control Register (INT2CR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-31   |

| 5.27   | INTerrupt 0 Status Register (INT0SR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-32   |

| 5.28   | INTerrupt 1 Status Register (INT1SR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-34   |

| 5.29   | INTerrupt 2 Status Register (INT2SR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-34   |

| 5.30   | Interrupt Timing 0 Control Register (IT0CR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-35   |

| 5.31   | Interrupt Timing 1 Control Register (IT1CR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-36   |

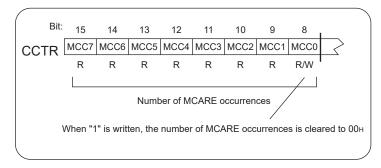

| 5.32   | Care CounTer Register (CCTR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-37   |

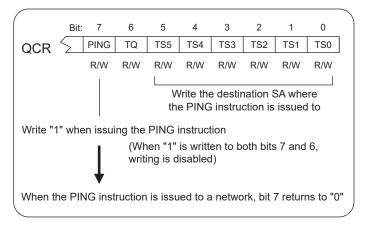

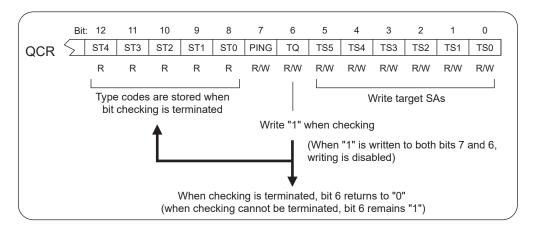

| 5.33   | Query Control Register (QCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-38   |

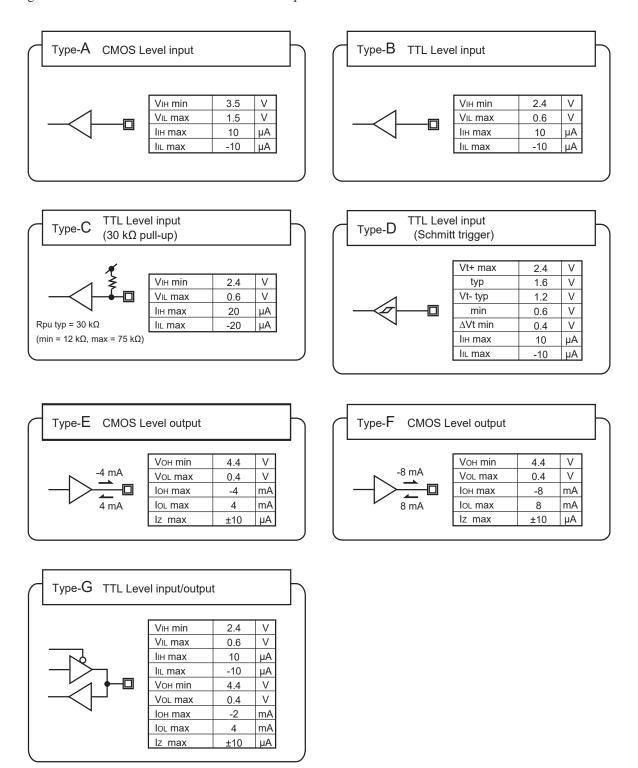

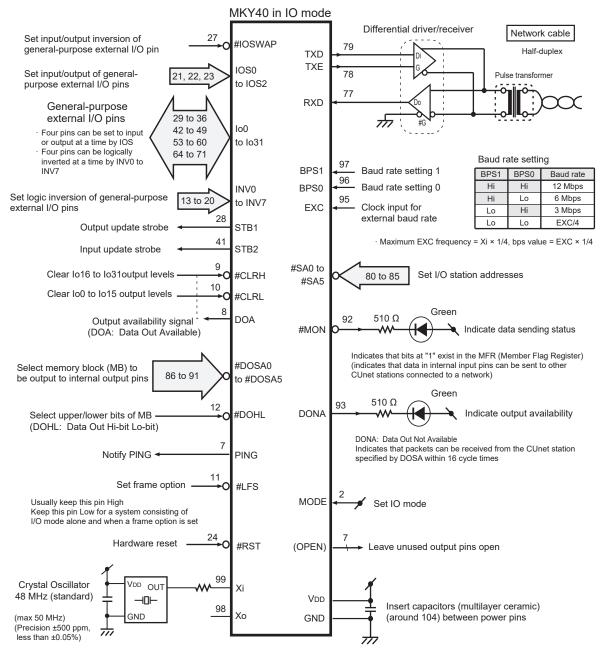

| Chapte | er 6 Hardware in IO Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 6-3  |

| •      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| Chapte | er 7 Operation and Connection in IO Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

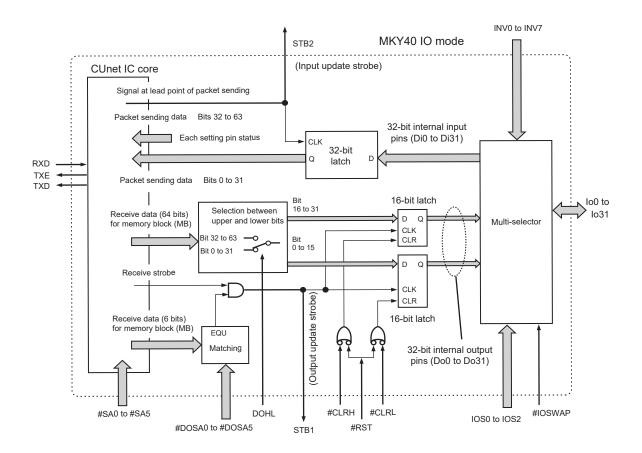

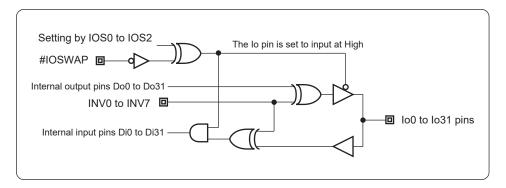

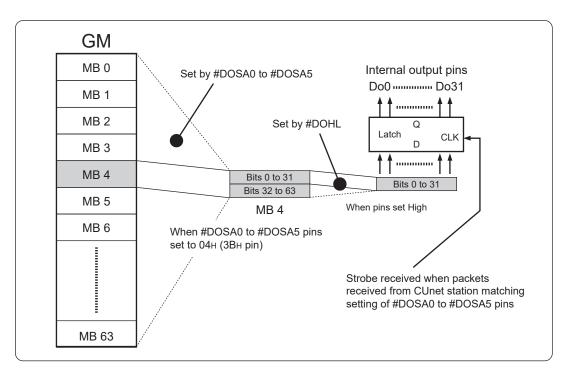

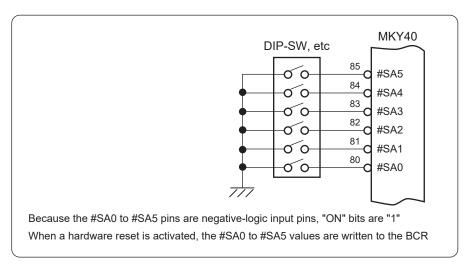

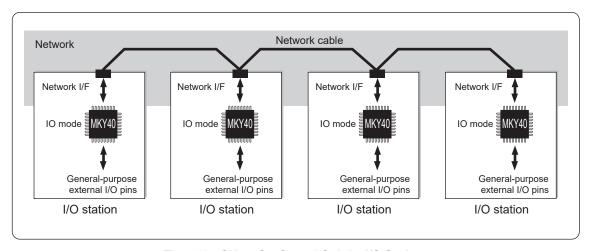

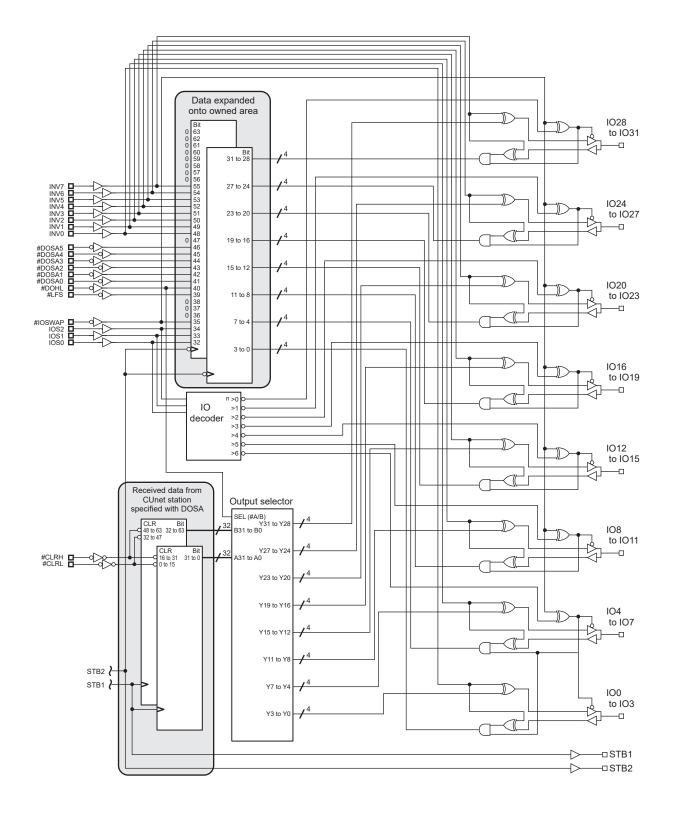

| 7.1    | Internal Configuration of MKY40 in IO Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7-4    |

| 7.2    | Operation in IO Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7-5    |

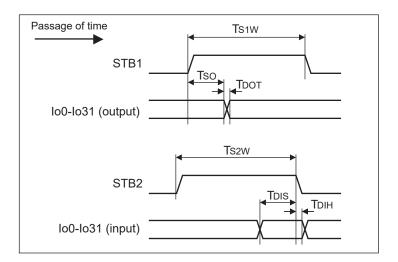

| 7.2    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| 7.2    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| 7.2    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| 7.2    | The state of the s |        |